作者:歐敏銓

當全球雲端巨頭都在尋找除了 Nvidia 以外的AI運算解方時,聯發科AI ASIC脫穎而出。「市場看重的不是聯發科『會做 AI』,而是看重它『能幫大客戶省錢、提高效率、去 Nvidia 化』。」

在全球半導體產業的版圖中,聯發科(MediaTek)長期以來被貼上「手機晶片供應商」的標籤。然而,近年來這家台灣 IC 設計龍頭的評價出現了質的飛躍。市場不再僅僅關注其天璣系列手機晶片的銷量,更將目光鎖定在其高速成長的 AI ASIC(特殊應用積體電路)業務上。

為何 AI ASIC 服務會成為聯發科最火熱的增長引擎?這背後不僅僅是「代工」兩字可以概括。要深入理解這場轉型,我們必須從技術架構的本質差異,到商業模式的深層變革進行全面拆解。

定位差異:為什麼NPU與AI ASIC不能混為一談?

在一般的認知中,AI 運算往往與 NPU(神經網路處理器)掛鉤。但對於 Google、Meta、Microsoft 這些雲端巨頭(CSP)而言,電腦、手機等裝置內建的 NPU 只是「工具零件」,而他們真正需要的是「整套訂製服務」。

聯發科的定位在於:他們不只是賣你一顆「含有 AI 功能的處理器」,而是利用他們手中強大的 IP(矽智財)庫、SerDes(高速傳輸技術)及 先進封裝(CoWoS)整合能力,幫雲端巨頭量身訂做極具CP值的 AI 心臟。這是一種從零件供應商到系統架構師的身份轉變。以下是兩者的核心差異:

| 比較項目 | 一般 NPU | 聯發科 AI ASIC |

|---|---|---|

| 產品形式 | 晶片內部的一個功能模組(IP) | 根據客戶需求量身打造的整顆晶片 |

| 應用場景 | 消費級產品(手機、平板)。例如天璣 9400 裡的 NPU 負責拍照優化、即時翻譯 | 資料中心、雲端伺服器。例如為 Google 打造的 TPU,專門處理大規模 AI 訓練或推論 |

| 自主權 | 通用型設計,手機廠拿到什麼就用什麼 | 客戶(如 Google、Meta)參與設計,可去除不必要電路,達到極致效能與省電 |

| 商業模式 | 賣標準化晶片(產品銷售) | 賣設計服務與先進製程整合能力(設計費 + 權利金 + 晶圓代工) |

聯發科與台積電合作多年,對先進製程(3nm / CoWoS 封裝)非常熟悉。找聯發科設計,等於是買了一張進入台積電頂尖廠房的「保證通行證」。不僅如此,開發一顆頂級 AI 晶片的研發費用可能高達數億美元,聯發科可以幫客戶分擔開發風險。

核心價值的三位一體:省錢、提效、去Nvidia化

市場在評估聯發科的ASIC業務時,最常提到的關鍵字是「提效」。但在半導體的頂級殿堂裡,「提效」不僅僅是變快,而是包含以下三個層面的商業戰略:

1. 能效比(Performance per Watt)的極致提升:

對於擁有數十萬台伺服器的 Google 或 Meta 來說,電費是最大的營運負擔。聯發科透過客製化 ASIC,能幫客戶把不必要的電路(如手機用的通訊模組)全部移除,只保留 AI 運算的純粹結構。這種「精簡」能讓晶片在相同電力下,運算效率遠超通用型的 GPU,實現真正的綠色算力。

2. 研發時程(Time-to-Market)的高速化:

在 AI 技術迭代以「月」為單位的今天,慢一步就是輸。研發一顆 3nm 晶片動輒需要數年。聯發科手中擁有現成的「矽智財(IP)」,如同提供已經過安全驗證的建築模組,讓客戶能跳過基礎建設,直接進入核心演算法的開發。這讓開發周期大幅縮短,幫助客戶在最快時間內將算力上線。

3. 資料傳輸(Interconnect)的無縫提效:

AI 訓練最怕晶片與晶片之間通訊塞車。聯發科引以為傲的 SerDes 高速傳輸技術,就像是在晶片與晶片之間蓋起了超高速公路,解決了大規模運算時的數據瓶頸。

營收結構質變:為何資本市場願意給予更高估值?

過去聯發科的股價往往隨手機產業的景氣循環起伏。但 AI ASIC 業務的出現,徹底改變了其獲利模型。以下是支撐其股價衝刺的兩個核心邏輯:

1. 打入 Google TPU 供應鏈的標誌性意義:

聯發科成功切入 Google TPU (Tensor Processing Unit) 供應鏈。這不僅是訂單的獲取,更是技術實力的終極背書。這證明聯發科有能力處理 3nm、2nm 等尖端製程與複雜的 I/O 設計。過去這塊雲端 ASIC 市場主要由博通(Broadcom)與邁威爾(Marvell)壟斷,聯發科的加入象徵其已正式進入半導體設計的「頂級聯賽」。

2. 獲利含金量與高成長預期:

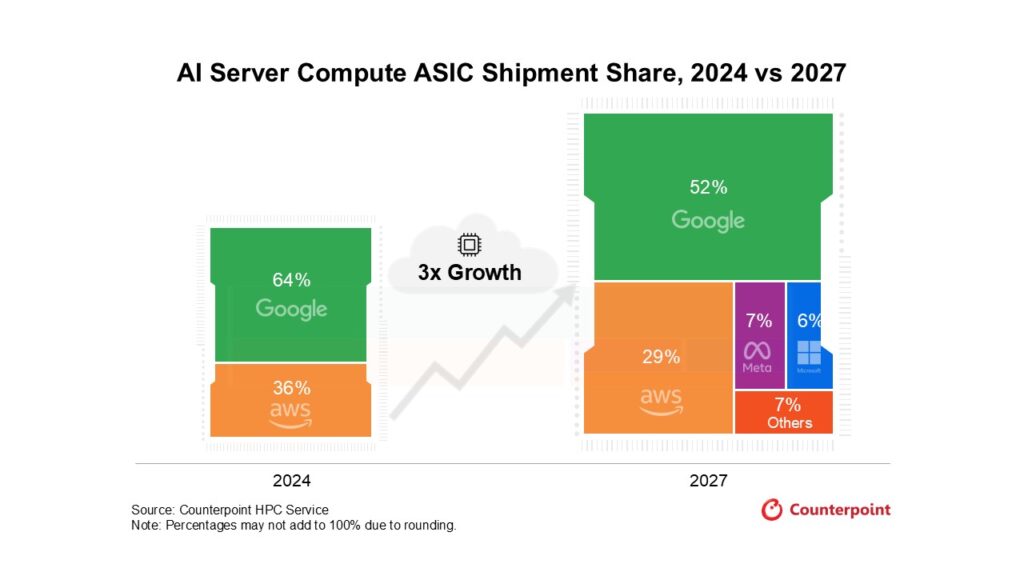

根據多間投行分析師(如 Morgan Stanley、花旗)的報告預期,聯發科 ASIC 業務在 2025 至 2026 年進入爆發期後,年度營收貢獻有望挑戰數十億美元級別。此外,根據Counterpoint 最新發佈的一份報告指出,全球AI伺服器運算ASIC出貨量,預計至2027年將較2024年成長三倍,這也是資本市場願意給予聯發科更高本益比評價的關鍵。。

不只是代工:解構「晶片建築師」的角色

很多人會混淆「晶片代工」與「ASIC 服務」。如果我們用蓋房子來比喻,台積電是「營造商」,而聯發科則是「頂級建築事務所」。

像 Google、Meta 雖然軟體實力極強,但要設計出能撐住 3nm 製程、低功耗、且不會燒壞的硬體結構,門檻極高。聯發科的核心價值在於提供現成的「地基」與「鋼筋」——即 SerDes 高速傳輸 IP 和電力分配模組。客戶只需專注於自己的 AI 演算法(房間裝潢),其餘複雜的物理結構與製程銜接全由聯發科處理。

| 模式 | 類比工業定義 | 在半導體界的實際操作 | 誰負責出「藍圖」? |

|---|---|---|---|

| OEM (代工) | 台積電 (Foundry) | 客戶把電路圖完整交給工廠,工廠純粹負責製造、封裝。 | 客戶 |

| ODM (設計代工) | 一般的 ASIC 公司 | 客戶提出功能需求,設計公司幫忙研發並找工廠做出來。 | 設計公司 |

| MTK ASIC | 「超強模組化」ODM | 雲端巨頭提供核心 AI 算法,聯發科提供高速傳輸、電力分配、先進封裝等基礎架構。 | 客戶核心 + MTK 框架 |

核心競爭力:Chiplet技術與IP護城河

隨著 AI 模型規模呈指數級增長,單一晶片(Monolithic SoC)已無法負荷。聯發科擁有的 Die-to-Die 互連技術,能將不同的運算單元(CPU、NPU、GPU)像樂高一樣組合成客製化大晶片。這種系統級(System-on-Chip/Package)的整合能力,正是大型雲端客戶最需要的。

此外,聯發科在行動端累積了 20 年「高效能又省電」的經驗。在 3nm/2nm 的先進製程下,晶片線路比頭髮還細幾萬倍,這時物理特性會變得非常混亂(散熱、訊號干擾、漏電),聯發科處理手機極端環境的設計經驗,轉化為雲端伺服器節能效率的關鍵優勢。

這種「技術護城河」使得客戶一旦採用聯發科的高速傳輸介面,更換供應商的風險與成本將高到難以想像,這讓聯發科從「逐單報價」的手機晶片商,變成了雲端巨頭的長期戰略夥伴。此外,當聯發科幫某位客戶開發的高速介面技術,稍作修改後可以賣給其他客戶。也就是說,晶片設計一旦開發完成,後續的邊際成本極低,利潤空間非常大。

結語

綜觀聯發科在 AI ASIC 領域的崛起,本質上是一場「技術紅利」與「市場缺口」的完美接軌。當 NVIDIA 的通用型 GPU 成為市場稀缺資源且成本高居不下時,雲端巨頭追求「算力自主」已成為不可逆的趨勢。聯發科在此扮演的角色,絕非單純的代工或組裝,而是憑藉深厚的矽智財積累與製程整合經驗,為大客戶解決了從算法轉化為硬體時最困難的「落地瓶頸」。

這種模式的成功,讓聯發科從過去依賴消費性電子景氣的「標準化零件商」,轉型為掌握雲端核心算力的「戰略合作夥伴」。其獲利模式也從單純的晶片銷售,進化為高毛利的技術授權與設計服務費。隨著 3nm、2nm 先進製程的推進,聯發科在 AI 基礎設施中的影響力將更具份量,這也正是資本市場重新定義其未來價值的底氣所在。

【延伸閱讀】

AI Server Compute ASIC Shipments to Triple by 2027 as Custom Silicon Enters Hyper-Growth Phase (Counterpoint分析報告)

- 聯發科 AI ASIC 服務為何這麼火?不只是代工! - 2026/05/06

- 【技術剖析】如何縮短機器人開發的Sim-to-Real鴻溝? - 2026/04/30

- 解析台灣「主權AI」國家戰略與行動 - 2026/04/28

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!