隨著各種新興AI應用對資料中心的算力需求持續攀升,相關技術架構也面臨顛覆性的變革。當基礎AI模型走向兆級參數、訓練叢集擴展至數萬顆CPU/GPU,「資料搬運」的效率成為決定系統擴展上限的關鍵因素,伺服器機櫃之間、內部晶片之間互連介面的頻寬、延遲與功耗表現,其重要性甚至高於運算元件本身的效能。

因此當市場資金大量投向AI基礎設施時,關注焦點不只是運算元件的演進,還包括資料傳輸介面技術是否能跟上腳步;這讓原本只是技術選項之一的共同封裝光學(Co-Packaged Optics,CPO)加速躍居主流。

以光路代替電路:從插拔式光模組走向CPO的必然性

高速互連技術發展最殘酷之處在於物理極限:當資料傳輸速率從 800G 走向 1.6T 甚至更高,銅線電路上的高頻訊號會面臨更嚴重的衰減、串擾與反射,為了把訊號「拉回來」,往往得加入更複雜的等化、重定時與佈線設計,結果就是功耗與發熱急遽升高。換句話說,速度越快、距離越長,純電路傳輸要維持訊號完整性的代價就越大。因此產業的共同趨勢是:在資料中心這類高頻寬、長時間運轉的場域,互連正逐步走向以光學傳輸取代電路傳輸——讓資料在更長的距離上盡可能用光纖/光路承載,只在晶片附近保留最短必要的電路段落。

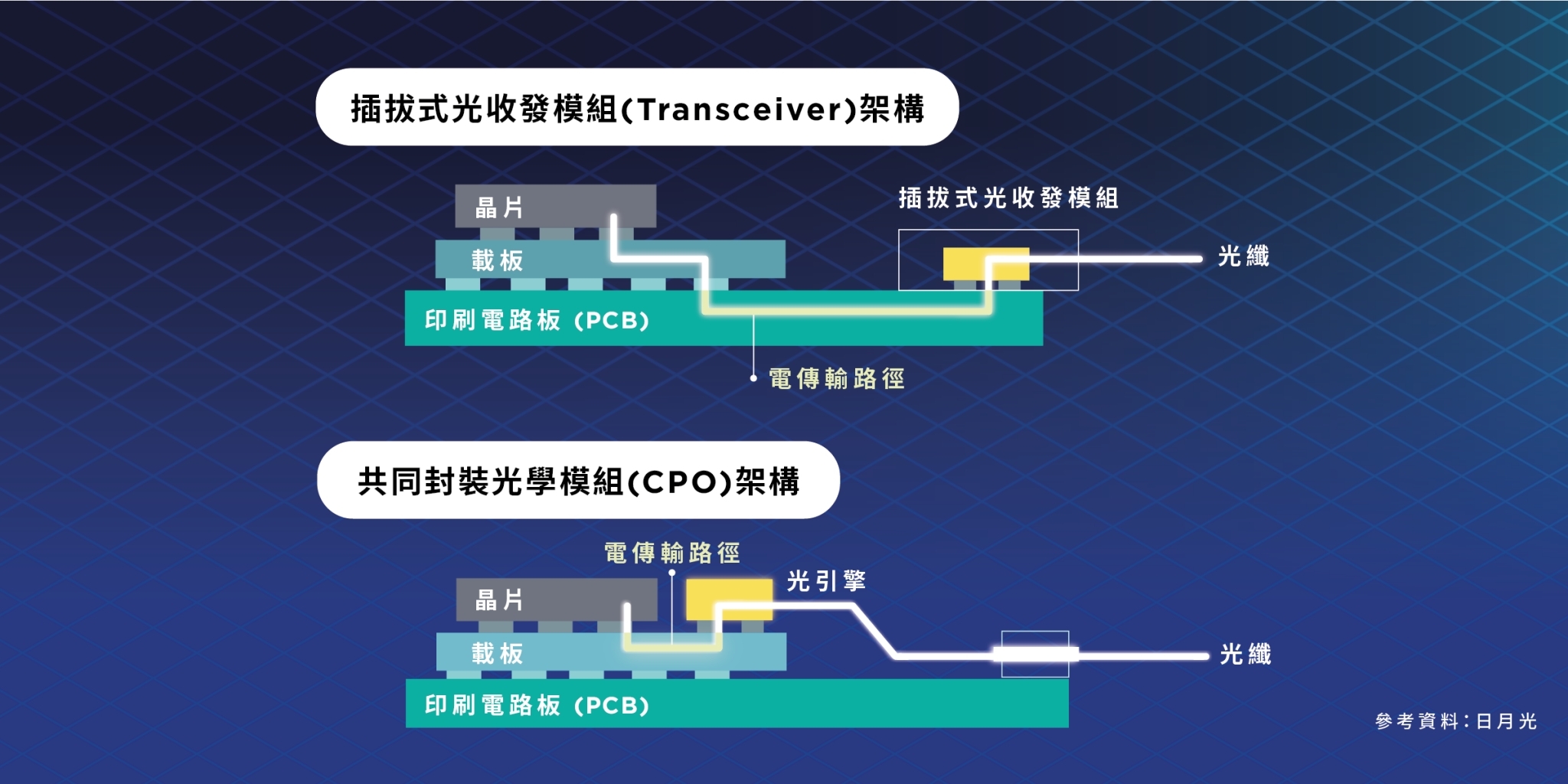

而插拔式光學模組(pluggable optics)是在過去十多年最成熟、也最廣泛採用的「電轉光」做法:把光收發器做成可插拔模組,讓交換器ASIC(或加速器)先用一段電介面把訊號送到前面板,再由模組完成電光轉換並接上光纖。它的優勢是維修方便、供應鏈成熟;但在更高速世代,結構性限制也開始浮現——問題不在光,而在「晶片到模組」之間那段仍必須走的高頻電路。當這段電走線拉到幾公分到十幾公分等級,為維持訊號完整性所需的等化與功耗會快速上升,連帶推高系統設計複雜度、壓縮可用連接埠密度,也讓散熱與機櫃電力配置更吃緊。

因此業界開始將目光轉向 CPO,也就是讓光學引擎更靠近晶片的解決方案。CPO並不只是把光學模組做得更小,而是重新切分電路與光路的分界點;在資料中心,光纖傳輸本來就負責長距離,但問題出在「晶片到光纖」之間必須先走一段電路。CPO的做法是將光電轉換位置從機殼前面板搬移到更接近晶片的位置——把光學引擎(矽光子晶片、調變器、探測器,以及封裝內的耦合結構)與交換器或加速器晶片封裝在同一基板上。

插拔式光學模組與CPO的架構比較(圖片來源:SEMI)

這能將讓原本較長的高頻電路徑縮短至毫米級,晶片輸出的高速電訊號只需要走很短一段,就能進入光學引擎完成「電→光」調變,接著用光纖把資料帶走;回程則由光學引擎把「光→電」轉回,送回晶片。電路縮短意味著損耗變小、等化需求下降、功耗更容易壓低;同時,把原本佔據前面板空間的光模組「內收」到封裝附近,也有利於提升整體頻寬密度,緩解封裝邊界(shoreline)帶來的I/O擁塞。

對資料中心營運商來說,CPO的價值在於能實現每位元功耗表現與連接埠密度更佳的系統,並因此能簡化散熱設計、降低整體持有成本(TCO),讓AI運算叢集在功耗可控的前提下,持續擴充互連規模,突破資料搬運帶來的瓶頸。

產業局勢速寫:CPO 是跨域整合賽,供應鏈分工正在重組

目前CPO的整體應用情況,仍處於業界廠商已加快導入速度,但尚未全面放量階段,但在AI資料中心朝800G至1.6T傳輸速度演進的路徑上,已被視為最關鍵的下一代互連技術之一。CPO被視為目前市場基數雖小,但成長潛力看好的技術,如市場研究機構Mordor Intelligence估計,2026 年該市場規模約1.61億美元,可望在2031 年擴展至7.48億美元,期間年複合成長率(CAGR)可達35.92%。

從供應鏈來看,CPO是一場典型的「跨域整合」競賽,其中包含四大類玩家:第一類是交換器/網通晶片與平台端,掌握規格、導入節奏與採購話語權,代表性廠商包括Broadcom、Marvell、Intel,以及具系統影響力的Cisco;其中Broadcom已推出51.2Tbps CPO交換器平台,顯示 CPO 正從概念走向平台化。

第二類廠商是光學引擎/矽光子與光學I/O供應商,負責把「光」做成可封裝、可被系統整合的子系統,例如Ayar Labs主打光學I/O(Optical I/O)與光學小晶片(Chiplet)技術,期望以可封裝的光互連元件解決高頻寬資料搬運;Ranovus則擅長矽光子與共同封裝光學引擎/模組,針對資料中心與AI網路互連;POET Technologies則聚焦矽光子整合平台(如光學互連引擎/封裝平台),強調以封裝化/平台化方式整合光學元件,提升量產與系統導入可行性。

在這個類別與工具鏈的交界處,還有像是Lightmatter這樣的「平台型」新創公司,除光學互連/光子計算相關布局外,在CPO議題上更常被視為共同封裝光學平台與整合方案提供者,並透過與 Synopsys、Cadence等EDA/IP生態合作,把高速介面、設計流程與驗證方法納入整合路線,降低客戶導入風險、加速商用落地。

第三類是製造與先進封裝端,決定CPO能否跨過良率、可靠度與成本門檻;例如晶圓代工大廠台積電TSMC)的COUPE 被描述具備與主晶片形成共同封裝結構的彈性,是矽光與 CPO 路線的重要拼圖。 第四類則是EDA/IP 與多物理模擬工具鏈:CPO把高速 SerDes、封裝走線、光子元件與熱/應力拉到同一個設計問題裡,若缺乏已驗證的介面 IP 與可重複的協同設計/驗證流程,就難以規模化導入,因此設計工具也在其中扮演推進CPO技術演進的重要推手。

從可行性到規模化:2026 之後的觀察重點

接下來CPO要從「可行性」走到「規模化」,關鍵不在技術供應商的宣傳聲量,而在於相關解決方案是否能跨越可靠度、測試、維修性、良率與成本模型等門檻。首先是熱與封裝共存:CPO把光學引擎拉近交換器ASIC/加速器,等於讓光電元件貼近高熱源,必須解決溫度漂移、材料應力與耦合偏移,並與冷板/液冷等散熱方案協同設計。

第二是個挑戰是封裝後的測試與良率放大效應:光學耦合與校準流程更複雜、測試點更少,一旦良率下滑,就會被共同封裝放大成整體成本。第三是可維運性:插拔式模組若遭遇故障容易更換,但CPO封裝了關鍵光學元件,必須要重新安排故障定位、備品策略與現場更換流程,否則資料中心難以承擔停機風險。

要將市場規模擴大,還需跨過標準化與供應鏈平台化:從光學引擎介面、封裝型態到連接/耦合規格,若仍高度客製,就很難形成規模經濟;而外部雷射光源(ELS)等架構雖可把雷射與高熱源分離,也會帶來光功率管理、冗餘與監控等系統課題。

總結而言,CPO 不會一夕取代舊有插拔式模組,而是從交換器端加速成熟,再逐步往加速器互連深化;其未來大規模部署的關鍵,取決於產業界能否把它從「概念驗證」推進到「可量產、可維運」的系統工程——也就是建立一套可複製的設計、製造、封裝、測試到維運流程,並在可靠度、良率、可維修性與成本模型之間取得平衡。當這些條件到位,CPO才不只是少數高階機種的亮點,而會成為新一代AI資料中心的關鍵基礎。

(責編:Judith Cheng)

- 從資料到部署一站加速:研華攜手Edge Impulse降低Edge AI開發門檻 - 2026/04/27

- 聯發科帶領產業邁入「AI定義汽車」新時代 - 2026/04/27

- 全球AI光收發模組市場高速成長 關鍵零組件供應吃緊 - 2026/04/23

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!