作者:Bird

終於進入到通訊界面這系列介紹的最後一塊 — I2C(也寫成I2C)。I2C 雖然只有簡單的兩根線,但它大概是我們聊過的通訊界面中最複雜的一種,它在這兩根線上可做到 multi-master、multi-slave 的多裝置通訊,還有著極爲巧妙的同步、協調以及錯誤處理機制,因此我們會花比前面兩個界面更多的篇幅來介紹它。

也是歷史悠久 #

I2C 和 SPI 的歷史一樣悠久,可以回溯到 1980 年代初期。當美洲大陸的 Motorola 發展出 SPI 時,遠在歐洲的荷蘭商飛利浦半導體公司爲了解決電視機及顯示器內部許多週邊 IC 之間的通訊問題,而發展出 I2C bus 這個標準。

I2C 是「inter IC communiction」的意思,也就是 IC 與 IC 中間的通訊界面。IC 是「Integrated Circuit」,指的是 I/O 擴展器、ADC、DAC 等週邊晶片,雖然 IC 本身也是一個縮寫字,但並沒有人把 I2C 寫成「IICC」,英文念法則是「I-square-C」,也就是那個小小的 2 是 I 平方的意思,中國大陸則習慣稱之爲「I 方 C」。

飛利浦爲 I2C 申請了專利,也註冊了商標,因此實務上要使用 I2C 技術必需要取得飛利浦半導體的授權並支付權利金。早年一些半導體公司爲了使用 I2C 技術卻又不願意支付權利金,便實作一些與 I2C 相容但又不完全一樣的設計,也另外取了一個不一樣的名字,以免侵犯到飛利浦半導體的商標權,因此常常看到的「2-wire bus」之類的界面名稱,其實多半是沒有付錢的 I2C bus 界面。

不過專利總有到期的一天。I2C 的美國專利(編號 US4689740A)在 1987 年獲得核准,而在 1995 年之前獲得核准的美國專利效期爲 17 年,因此 I2C 的美國專利在 2004 年到期。事實上飛利浦半導體曾經在 2000 年和 2001 年對數家美國的大型半導體公司發動專利訴訟,爲的就是 I2C 的使用授權,而當年台灣也有好幾家主機板製造商被捲入這場訴訟。

2006 年飛利浦拆分旗下的半導體公司,並獨立出 NXP(恩智浦)半導體,I2C 的商標及相關權利便由 NXP 半導體繼承,另外也由於專利已過期,使用 I2C 相關的技術已不再需要取得 NXP 的授權,但如果要使用 I2C 的商標、名稱,或是分配正式的 I2C address,仍然要付錢給 NXP。

I2C 的實體界面 #

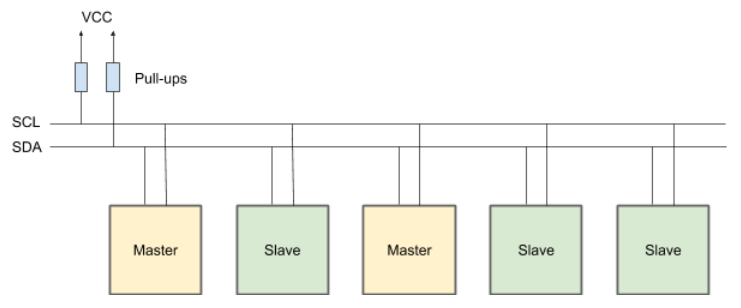

I2C 的實體界面只有兩根訊號,分別稱之爲 SCL(serial clock)與 SDA(serial data),而由於 I2C 是一個 bus,在這個 bus 上所有的裝置都得透過這兩個訊號相連,也就是說 I2C 只需要兩根訊號線,就可以讓很多(多達上百個)裝置彼此之間互相通訊。

(圖片來源:Bird 提供)

上圖是一個典型的 I2C bus 電路,bus 上的所有裝置都透過 SCL/SDA 這兩根線相連。I2C 允許 bus 上可以有多個 master、多個 slave 存在,只要彼此的 address 不衝突、裝置數量沒有超過 bus 的電氣特性上限就沒有問題。

在這個電路中,有兩個小小的電阻,分別將 SCL 和 SDA 拉到 VCC。這兩顆電阻稱之爲 I2C bus 的「拉起電阻」(pull-ups),看起來好像沒什麼複雜的地方,但它們卻是 I2C bus 能正常運作的關鍵。

巧妙的 Wired-AND #

要了解 I2C bus 的工作原理,就要從裝置驅動 bus 的方式說起。

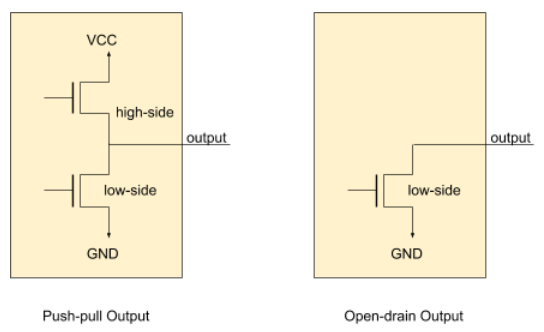

I2C bus 上所有的裝置都是透過 open-drain 或 open-collector 的方式來驅動 SCL 或 SDA。一般 push-pull 的數位邏輯輸出電路會有 high/low 兩顆電晶體,各自負責把輸出拉到 high 或 low 的工作,但 open-drain 或 open-collector 的輸出則只有 low-side 一顆電晶體。

(圖片來源:Bird 提供)

從上面的電路可以看出,因爲 open-drain 輸出電路只有 low-side 一顆電晶體,它只能把輸出拉到 low,無法把輸出變成 high,因此當 open-drain 輸出的 low-side 電晶體不導通時,它就會呈現 high-Z 的高阻抗狀態,就好像它沒有接到任何東西一樣。

每個裝置都是 open-drain 輸出,再加上拉起電阻,每根線的電路就變成這樣:

(圖片來源:Bird 提供)

這個電路的特性是:

- 當所有的裝置都輸出 high 時,bus 上的狀態才會是 high

- 只要有任何一個裝置輸出 low,bus 上的狀態就會是 low

這樣的電路稱之爲「Wired-AND」邏輯,它的意思是用電路連接(wired)構成的 AND 邏輯。AND 邏輯電路的特性是:只有當所有的輸入爲 1 時,輸出才會是 1;只要有任何一個輸入是 0,輸出就會是 0。有沒有覺得這樣的特性和上面的電路描述很像?這就是它被稱之爲 Wired-AND 的原因,I2C bus 上的所有裝置,就是靠著 Wired-AND 的邏輯連接在一起的。

在上面這張圖中,除了驅動 open-drain 輸出的電晶體外,還有一個白色的小三角形,它是 I2C 訊號的輸入緩衝器;不管是 SCL 還是 SDA,事實上都是雙向的接腳,而且是所謂的「quasi-bidirectional」接腳。

雙向就雙向,還有什麼真的假的?一般 IC 上的所謂的 bi-direction 接腳,可以在輸出和輸入模式之間切換,但 I2C 的接腳是「同時」是輸出也是輸入;當它在輸出時,同時也透過輸入緩衝器在監聽這接腳上的狀態。

爲什麼要監聽呢?正是因爲這個 bus 的 Wired-AND 特性。當你輸出 low 時,bus 上一定是 low,但是當你輸出 high 時,bus 上卻不一定是 high,只有當其它所有的裝置都輸出 high,而且你也輸出 high 時,bus 才會是 high,如果有任何一個其它裝置輸出 low,即使你輸出 high,bus 的狀態也會是 low。

因此當我們在輸出 high 時,藉由監聽 bus 的狀態,可以得知是不是有其它的裝置在輸出 low,這個特性對 I2C bus 的 clock 仲裁非常有用,我們之後會再詳細說明。

至於拉起電阻的大小,也是 I2C bus 電路設計上一個很重要的參數,因爲所有的裝置都只能把 bus 拉 low,當它們都不拉 bus 時,就要靠拉起電阻把 bus 拉到 high。這個電阻放得太大,拉 high 的速度會很慢,影響到 bus 高速運作的穩定性;放得太小,又會擔心裝置的驅動能力不夠,無法把 bus 拉得夠地,因此拉起電阻的計算往往是 I2C bus 設計時很重要的過程,我們後面也會詳述。

小結 #

這次我們簡單介紹了 I2C bus 的歷史以及從飛利浦半導體到 NXP 恩智浦半導體這一路以來關於 I2C 的專利戰,同時也說明了 I2C bus 的實體電路以及它用 Wired-AND 邏輯運作的特性。

下一回,我們將進入 I2C 的通訊協定,繼續聊聊這個界面的通訊邏輯。

(責任編輯:賴佩萱)