作者:Judith Cheng

不久前晶圓代工業者GlobalFoundries宣佈與新思科技(Synopsys)達成最終協議,將收購後者旗下的ARC處理器IP解決方案業務與相關工程團隊,並以加速「實體 AI」布局(physical AI)、強化客製化矽晶片能力為目標。促成這樁收購案的主要因素自然是商業考量,不過更讓人覺得有趣的是:在2000年代初期一度因系統級晶片(SoC)風潮而備受矚目,後來的發展幾乎可以說是「顛沛流離」的ARC、MIPS處理器核心,不但隨著AIoT /Edge AI與實體AI等應用崛起找到可發揮的新舞台,還即將成為一家!

邊緣端AI應用讓RISC系列處理器成為主角

相較於能支援更大算力、在當紅雲端資料中心基礎設施中扮演主角的x86處理器(Intel 與 AMD 雙雄),具備一定程度算力,但在功耗、成本上更「輕量」的精簡指令集(RISC)架構系列處理器,或許因為大多「隱身」在市場上不同供應商的SoC/ASIC 之中,而且分散在五花八門的各種嵌入式、物聯網(IoT)應用,而顯得低調許多。

隨著AI發展從雲端向邊緣擴散,終端裝置不再僅是感測與連網的資料入口,而必須具備本地推論、控制與即時反應的能力;而有許多邊緣AI應用(特別是由IoT升級的較小型專案)的核心考量並不在於追求極致算力、或是能跑多大的AI模型,更著重於在「足夠的推論效能」與「可接受的功耗表現」之間尋求最佳平衡,具備多樣化選擇、高度客製化彈性的RISC系列處理器自然成為主角。

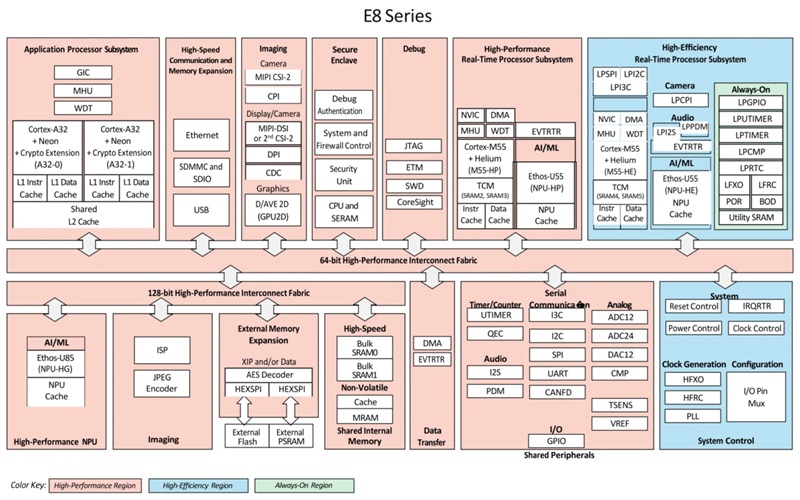

邊緣AI最消耗能量的任務不只在「模型推論」,而是分散在前後處理與系統控制,例如影像/音訊資料搬移、濾波與特徵抽取、感測融合、通訊與安全加解密、以及即時控制迴路等;這些工作不追求高算力,更在意長時間穩定運作、低延遲,以及用更精簡的運算步驟與記憶體空間完成任務。因此,邊緣裝置SoC 大多採用由CPU搭配 DSP/NPU 加速器的協同架構——其中CPU端不僅多半採用RISC架構,也往往是由多個核心(甚至不同叢集/分工層級)共同組成:以加速器處理高重複性的運算,並由這些RISC系列CPU核心分別負責任務排程、資料搬移與記憶體管理,並在加速器不擅長的流程中靈活補位。

採用多CPU核心+NPU異質運算架構的ALIF E8 Edge AI SoC。(圖片來源:ALIF)

為了更進一步提升系統效能,部分晶片更導入 ASIP(專用指令集處理器)方法,在保有軟體控制彈性的同時,將最耗時的運算設計成專用指令或電路路徑,讓處理器以更少步驟完成資料整理、向量運算等任務,進一步降低功耗。這種異質運算分工模式能以最佳化的系統成本,將分散的運算需求串聯成完整的推論流水線,落實為可穩定運作、大量生產的終端使用者體驗;從AIoT到Edge AI,再到更強調感知-決策-動作封閉迴路的「實體 AI」(例如機器人),當AI越靠近應用現場、越受限於功耗與成本,RISC系列處理器越是不可或缺。

通用CPU:Arm與RISC-V核心居主流

早期嵌入式系統多以單一MCU處理所有工作,但隨著多媒體、連線與安全需求變複雜,開始出現把「即時控制」與「高階作業系統(OS)/應用程式」分開運作的SoC,並逐步形成由多核心CPU分層承載不同任務的架構;而在行動裝置與IoT終端,Arm推廣的big.LITTLE概念更進一步把「高效能核心+高能效核心」的分工模式商品化與普及,讓系統能在效能與功耗之間動態切換。

近年AI被導入邊緣裝置後,NPU/DSP 進一步加入,CPU端也更常以多核心、甚至多叢集方式分層負責OS與應用、通訊協定與安全、電源管理與即時控制,並把資料流與工作排程串起來。也因此,邊緣AI應用的處理器核心競爭不只看單一核心有多快,而是整套異質運算分工能否在功耗與成本限制下,穩定提供所需的使用體驗。

在各種RISC系列處理器核心中,Arm在目前的多數邊緣端應用中佔據最大宗,其優勢在於「從 MCU到應用處理器」的產品線完整度,以及長年累積的工具鏈、作業系統與軟體生態,使其在AIoT/ Edge AI或新興實體AI專案上能以較低風險、較快節奏進入量產。畢竟對許多終端產品而言,CPU的價值不在單點性能,而在能否穩定支撐驅動、通訊協定、安全更新與系統維護;這正是 Arm長期穩居市場主流的原因。

RISC-V 處理器核心則展現了截然不同的戰略吸引力。這套起源於 2010 年美國加州大學柏克萊分校的指令集,憑藉其「開放標準 ISA」的特質,徹底打破了傳統授權架構的限制,賦予SoC設計者更高的自主權——開發者能靈活選擇現成核心或投入自研,並將產品差異化集中於指令集擴充(Extension)、記憶體子系統與安全機制的創新。這種進一步把「授權與供應鏈彈性」轉化為長期成本與產品線策略的優勢,對成本敏感、高度客製化,且需要在多元產品線間共享技術資產的邊緣AI應用來說特別理想,然而供應商能否在提供硬體靈活性的同時,同步構建成熟的軟體堆疊與生態系相容性策略,以降低開發者導入難度,會是成敗關鍵。

生態系逐漸壯大的開放性RISC-V核心陣營。(資料來源:RISC-V International)

可配置處理器與工作負載導向核心:Xtensa、ARC與MIPS

CPU之外,邊緣AI更吃重的是前後處理與常開任務的能效,因此Tensilica/Xtensa與ARC 這類「可配置處理器/DSP」路線仍有其獨特位置。Tensilica 是 1997 年誕生於美國矽谷的處理器 IP 公司,主打可配置/可擴充的Xtensa處理器架構,讓客戶能針對特定工作負載加入自訂指令與資料路徑,以提升能效與差異化。2013年,EDA 供應商 Cadence 宣布收購Tensilica,將 Xtensa/HiFi 處理器核心納入旗下,常被用在音訊、語音、視覺與感測融合等資料流工作負載,擅長以 DSP/向量化手段在小面積、低功耗下提供穩定運作,適合長時間開啟的應用場景。

ARC(Argonaut RISC Core)與Arm同樣起源於英國,1996 年左右由Argonaut Games團隊發展並衍生出商用處理器IP路線,後續以ARC International之名運作;2009年被Virage Logic收購,隔年(2010)Virage Logic又被 Synopsys 收購,ARC因而併入後者的DesignWare Processor IP 產品線,近年再延伸推出ARCv3與相容RISC-V的ARC-V家族,接下來將轉至GlobalFoundries旗下。

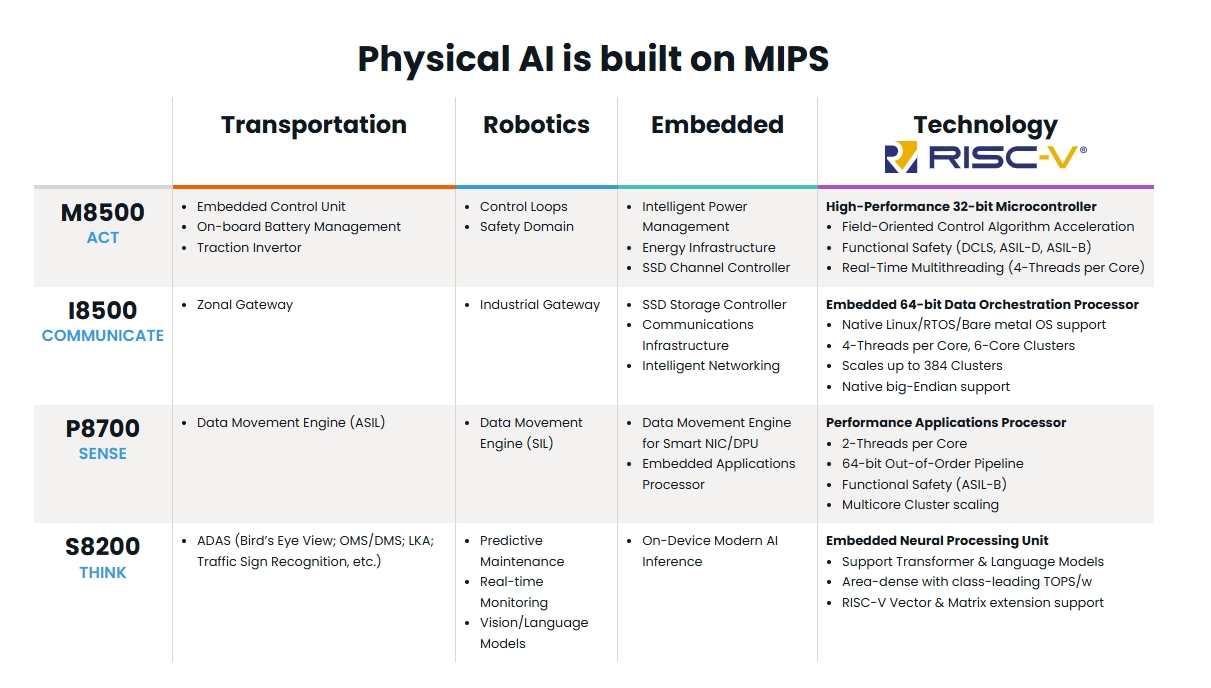

至於MIPS,1985年即作為經典RISC架構處理器問世,後續在產業整併中多次易主:2013年由Imagination Technologies收購,2017 年再出售給Tallwood Venture Capital,2018 年轉手Wave Computing;Wave於2020年申請破產重整後,MIPS於2021年重新出發、宣布轉向 RISC-V,並推出eVocore系列IP,又在2025年初針對實體AI應用推出Atlas平台(包括Sense/Think/Act),強調將即時運算、功能安全與資安、軟體堆疊整合成可導入的運算子系統(如 M8500/I8600/S8200),並提供開發與驗證環境,協助加速機器人、車用與工業自動化系統的應用落地。MIPS在2025年7月由GlobalFoundries完成收購。

MIPS針對實體AI應用推出的相關解決方案。(圖片來源:MIPS官網)

持續變化的RISC生態:完整平台化配套方案將是勝出關鍵

根據GlobalFoundries宣佈收購ARC的官方新聞稿內容,這家晶圓代工業者的計畫是將包括ARC-V、ARC-Classic、ARC VPX-DSP與ARC NPX NPU產品線,以及ASIP Designer 與ASIP Programmer等ASIP相關工具,還有ARC的專業團隊與旗下MIPS進行整合,建構針對實體AI應用量身打造的處理器IP解決方案,並將透過IP授權與軟體服務等方式深化與客戶的合作,協助加速產品上市時程。若整合順利,對Edge AI與實體AI領域的最大影響,可能在於把「客製化」從高門檻的少數專案,變成更多產品可負擔的常態選項。

未來無論機器人、工業自動化或車用邊緣平台,都要在功耗、成本、即時性與安全性間精準權衡。因此,具備RISC 核心、DSP/NPU、ASIP 客製能力及完備工具鏈的供應商,更能加速應用落地。邊緣側應用也不會由單一CPU決定勝負,會透過多核心分工,協同DSP/NPU甚至LPU等加速器的異質架構運作。因此對開發者來說,最關鍵的需求則是一套能實現元件協調、且具備可重複導入價值的系統化/平台化解決方案,而非處理器本身。針對不同處理器核心的現況與未來發展,MakerPRO持續關注!

|

架構家族 |

典型定位 (Edge AI/AIoT) | 商業授權模式趨勢 (2026 更新) |

參考連結 (授權與商務資訊) |

| Arm | 全場景主控核心:從低功耗感測器至高效能邊緣伺服器。 | 預交授權費 + 階梯式權利金。推廣 Arm Total Access (ATA) 與 Flexible Access,降低初期導入門檻,但長期依賴其軟體生態。 | Arm 授權模式說明 |

| RISC-V | 高客製化 SoC:成本敏感型 AIoT、特定領域加速器(DSA)。 | 開放 ISA (免費) + 商用 IP 授權。標準本身免費,但商用核心(如 SiFive, Andes)則收取設計 IP 與技術支援費,強調無供應商鎖定。 | RISC-V International說明 |

| Synopsys ARC | 嵌入式控制與 DSP:即時性高、功耗極低的 AI 邊緣端點。 | 商用 IP 授權 (即將併入 GF)。傳統隨 EDA 工具捆綁,2026 年起將整合至GF旗下MIPS業務,推向「IP + 製造」深度綁定模式。 | Synopsys ARC IP 產品組合 |

| Cadence Tensilica | 專用資料流處理:音訊視覺、感測融合與 Always-on 監控。 | 工具鏈授權 + 核心授權。提供獨有的 TIE (Tensilica Instruction Extension) 工具授權,讓客戶自訂指令集,以軟硬體整合套件形式收費。 | Tensilica 處理器 IP 方案 |

| MIPS (GF) | Physical AI 與車用:鎖定即時控制、高可靠性與物理 AI 平台。 | 平台化/子系統授權。併購 ARC 業務後,GF 提供包含 RISC-V 核心、軟體堆疊與晶圓代工優化的「一站式平台」授權。 | MIPS 官網最新動態 |

- 重磅宣告「邁入新階段」:Arm開賣AI資料中心CPU晶片 - 2026/03/25

- ADI:AI正加速邁向「實體智能」 - 2026/03/13

- 開拓GaN元件低電壓應用新戰場 EPC準備在AI時代大顯身手 - 2026/02/03

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!