作者:Bird

上一回我們介紹了 DRAM 的技術與架構,以及與 DRAM 高度相似的 NOR flash 記憶體結構。這一回我們要來看看另一個 flash 記憶體的結構:NAND flash,以及它爲什麼可以將 flash memory 的密度再度提高到另一個境界。

Flash 的儲存結構

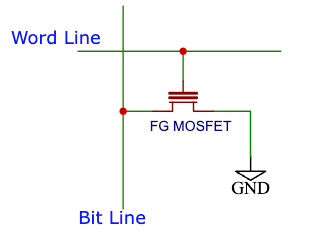

打從 EEPROM 發明開始,flash 記憶體的儲存原理就沒有太大的變化,它都是利用被困在 floating gate 裡無處可去的電荷狀態來控制 MOSFET 是否可以被閘極電壓控制,進而在電源消失之後仍然保持狀態。

(圖片來源:Bird 提供)

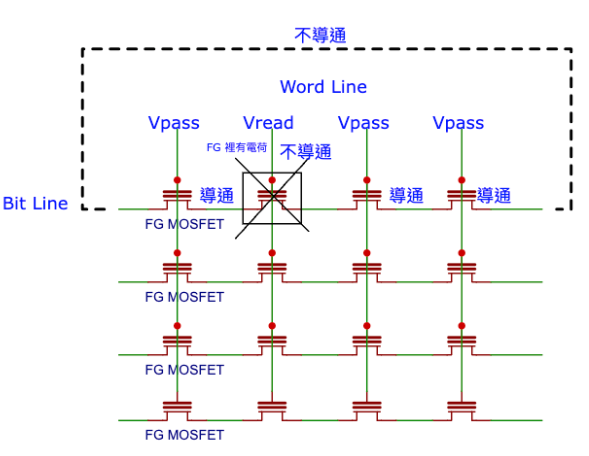

上圖是一個簡化過的典型 flash 記憶單元。當我們要讀取這個單元的內容時,我們就在 word line 上施加電壓;如果這個記憶單元裡的 MOSFET,它的 floating gate 裡沒有電荷,那麽加在 word line 上的電壓就可以透過 MOSFET 的閘極將通道建立,讓 MOSFET 的 source 和 drain 導通,MOSFET 一旦導通,bit line 上就可以感測到 MOSFET 另一端的狀態,也就是 ground。

如果它的 floating gate 裡有電荷,這個電荷形成的電場就會干擾閘極形成的電場,讓閘極無法控制 MOSFET 的通道開啟。這時,即使我們在 word line 上施加足以讓 MOSFET 導通的電壓,也無法讓它導通,所以 bit line 就感測不到 MOSFET 另一端的狀態。

換句話說,flash 記憶體的每一個單元所儲存的狀態,是藉由感應 word line 能不能控制 MOSFET 來決定的,而不是直接去感測 floating gate 裡的電荷狀態。

把儲存單元串起來

話說舛岡富士雄發明了 NOR flash,並被 Intel 看上將之商品化之後,他又繼續研究提高 flash 記憶體密度的更多可能。就在 Intel 量產 NOR flash 的前一年,舛岡富士雄又在 IEEE 國際電子組件會議(IEDM)上發表有關快閃記憶體的論文:《New ultra high density EPROM and flash EEPROM with NAND structure cell》。

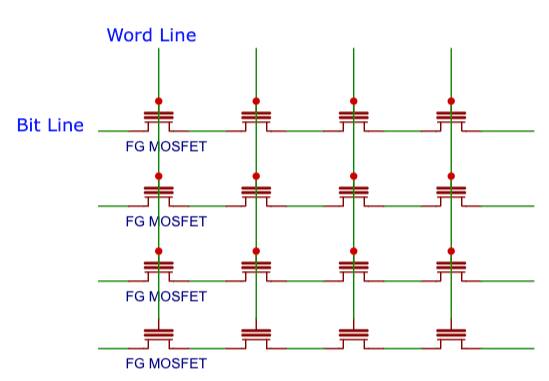

這種 flash 也使用一樣的儲存單元,但是它裡面的儲存單元安排並不是像 DRAM 那樣可以一個一個用 word line 選擇、用 bit line 讀取,而是一排一排串起來的。

(圖片來源:Bird 提供)

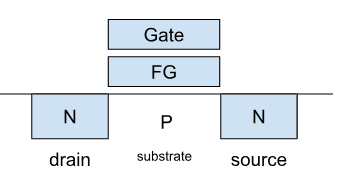

上圖是一個 4-bit x 4-word 的 NAND flash 結構。

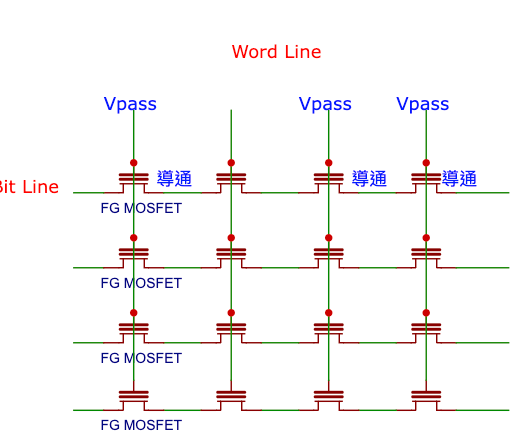

假設我們現在要讀取第二個 word 、第一個 bit 的內容,我們會在除了第二個 word 以外其他的 word line 上,加上一個電壓,叫做 Vpass。這個電壓夠高,高到不管 MOSFET 的 floating gate 上有沒有電荷,都可以讓 MOSFET 導通。

(圖片來源:Bird 提供)

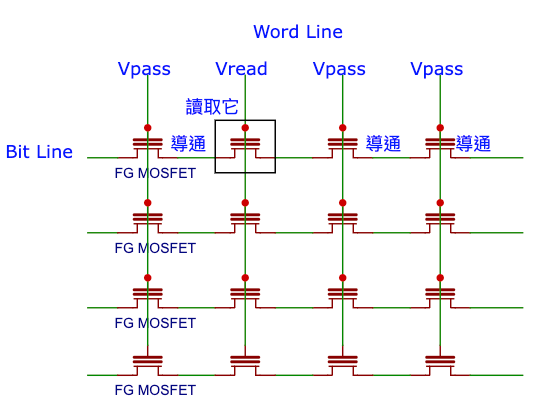

同時,我們在要讀取的那個 word 的 word line 上,施加一個沒那麼高的電壓,叫做 Vread。由於 Vread 沒有 Vpass 那麼高,因此 Vread 能否讓 MOSFET 導通,就取決於 MOSFET 的 floating gate 裡面有沒有電荷。

(圖片來源:Bird 提供)

如果這個 bit 的 MOSFET,它的 floating gate 裡有電荷,Vread 就沒辦法讓 MOSFET 導通,而同一條 bit line 所有的 MOSFET 是全部串聯在一起的,這時即使同一條 bit line 上所有其它的 MOSFET 都導通,但這一刻不導通,就會讓整串 bit line 都不導通。

(圖片來源:Bird 提供)

如果這個 MOSFET 的 floating gate 裡沒有電荷,Vread 可以讓 MOSFET 導通,而由於串聯在一起的其它 MOSFET 都被 Vpass 給弄通了,所以只要這個 MOSFET 導通,這一整串 bit line 就導通了。

因此,NAND flash 的讀取,其實就是利用串聯電路的特性,來偵測其中一個 MOSFET 導通與否,要讀取的那個 word,就在 word line 上施加可以讓 floating gate 作用的 Vpass,而其它的 word 就施加可以直接讓 MOSFET 導通的 Vpass。

但為什麼這種結構可以讓 NAND flash 的密度比 NOR flash 高出許多呢?

串聯的秘密

這是一個 floating gate MOSFET 長在晶片上的斷面結構:

(圖片來源:Bird 提供)

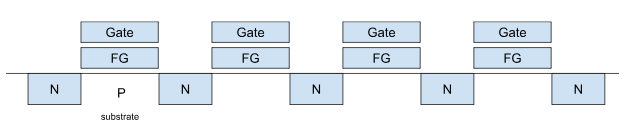

在 P 型半導體的 subtrate 上,長出兩個 N 型的區域,分別構成 MOSFET 的 source 跟 drain。事實上,在晶片的結構中,MOSFET 的 source 和 drain 這兩塊區域是完全一樣的。

因此舛岡富士雄就想到,既然構成 source 和 drain 的 N 型半導體區域是一樣的,然後我們又要串連相鄰的兩顆 MOSFET,那不如…

(圖片來源:Bird 提供)

前一顆 MOSFET 的 source,就是下一顆 MOSFET 的 drain。注意哦,不是連接到下一顆 MOSFET 的 drain,而是它同時也就是下一顆 MOSFET 的 drain。

這個做法大大地提高了 NAND flash 相較於 NOR flash 的密度。因為在 NOR flash 中,每一顆 MOSFET 的 source 和 drain 都要分別連接到 bit line 和 GND,需要大量的金屬連接線,而這些金屬連接線在晶片上佔用的面積其實相當可觀。

於是,這種高密度結構的 NAND flash 就主宰了往後數十年的 flash 記憶體市場,我們今天用的 SSD、eMMC、SD 卡等 flash 記憶體產品,幾乎都是 NAND flash 的天下。

小結

這一回我們說明了 NAND flash 的電路結構,以及它為什麼可以擁有高於 NOR flash 甚多的密度。下一回我們要繼續探討,NAND flash 這樣的結構,有沒有什麼弱點、代價,以及要如何克服這些問題。

(責任編輯:賴佩萱)

- 【Maker電子學】Flash 記憶體的原理與應用—PART22 - 2025/02/27

- 【Maker電子學】Flash 記憶體的原理與應用—PART21 - 2025/02/21

- 【Maker電子學】Flash 記憶體的原理與應用—PART20 - 2025/01/24

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!

2024/07/05

原文中:前一顆 MOSFET 的 source,就是下一顆 MOSFET 的 drain。注意哦,不是連接到下一顆 MOSFET 的 drain,而是它同時也就是下一顆 MOSFET 的 drain。這句:注意哦,不是連接到下一顆 MOSFET 的 「drain」括號裡的應該是source才對?