作者:Bird

上篇文章【Maker電子學】邏輯準位轉換電路的設計我們聊了如何設計邏輯準位的轉換電路,並用 SPI 界面示範了有特定方向的邏輯準位轉換電路;這次我們要來看看,對於傳輸方向可能會變化的邏輯電路,要如何設計它們的準位轉換電路。

驅動的方向

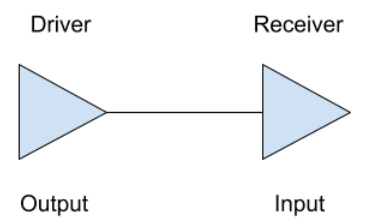

在數位邏輯電路中,「驅動的方向」是一個有點抽象的概念。所謂的「輸出」,或稱「驅動電路」,事實上就是一個比較強的電路,有能力去改變另一個電路的狀態;而所謂的「輸入」,或稱「接收電路」,就是一個很容易被改變狀態的電路,讓另一個電路可以輕易地操縱它。

輸出(驅動電路)與輸入(接收電路)(圖片來源:Bird 提供)

如果用比較厲害的語言來說,驅動電路通常是「低阻抗」,而接收電路通常是「高阻抗」。在電路學中,阻抗越高,狀態就越容易被改變,這也是爲什麽輸入電路的阻抗相對來説通常都很高,因爲如此才能讓別人輕易地改變它原先的狀態,也才能偵測到狀態的變化。

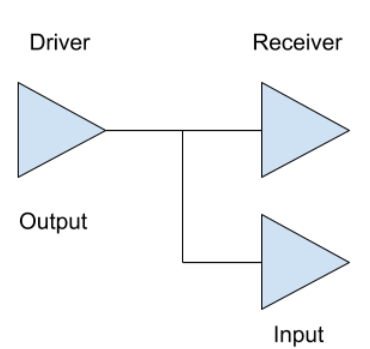

一個輸出電路,可以接到一個以上的輸入電路,因爲輸入電路是狀態很容易被改變的負載,因此「一對多」這樣的做法多半不會有什麽問題,如下圖所示:

(圖片來源:Bird 提供)

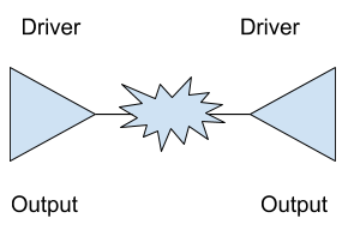

但如果我們將兩個輸出電路接在一起,由於輸出電路是一個很強勢、不願被別人改變狀態的電路,這樣的接法就會造成強強相碰,誰也不讓誰,在電路上叫做「port conflict」,意思就是界面打架了,如下圖所示:

(圖片來源:Bird 提供)

以上圖為例,如果左邊的 driver 輸出邏輯 1、右邊的 driver 輸出邏輯 0,那麽中間這根電路上的狀態到底是邏輯 0 還是邏輯 1 呢?這就得看誰強誰弱了。如果兩方的驅動能力有明顯的差別的話,強的一方可以取得主導權,但仍會造成電路耗電、發熱等不良的效應,但大部分的情況是兩邊的驅動能力都差不多,使得中間電路卡在一個不上不下的狀態,也就是我們之前説過的「你不要玩弄我」電壓。

可變方向的邏輯電路準位轉換 IC

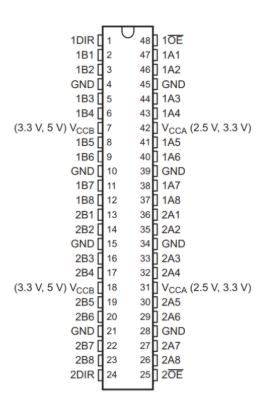

搞懂輸出與輸入的定義後,我們回到邏輯準位轉換的問題上。對於雙向都有需求的邏輯電路準位轉換,有一種很常用的可變方向轉換 IC,我們以 74LVC164245 爲例來説明,如下圖所示:

(圖片來源:Bird 提供)

74LVC164245 這顆 IC 分成 A、B 兩側,從接腳的命名上就看得出來;1A1、1A2、2A1、2A2 等就是 A 側,1B1、1B2、2B1、2B2 等就是 B 側;A 側和 B 側又再分成兩組,每組 8 支腳,因此每邊總共 16 支腳。A、B 兩側各有自己的電源接腳,分別是 VCCA 和 VCCB,而供電電壓分別決定了每一側的邏輯準位;其中 VCCA 支援 2.5 V 到 3.3 V 這種電壓比較低的邏輯準位,而 VCCB 則支援 3.3 V 到 5 V 這種電壓稍高的邏輯準位。

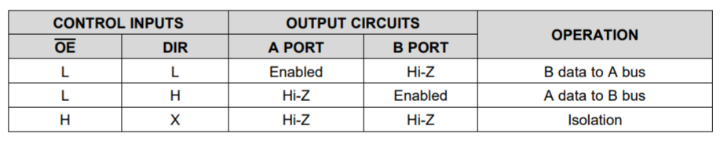

A 和 B 都可以當作輸入,也可以當作輸出,那麽誰是輸入誰是輸出呢?這時候就由 DIR 這支腳的狀態來決定了。我們來看一下 datasheet 中的接腳狀態功能表:

(圖片來源:Bird 提供)

當 DIR 腳是 low 的時候,它的功能叫做「B data to A bus」,意思就是傳輸的方向是由 B 到 A,這時 B 就是輸入、A 是輸出。從表上可以看出,此時 B 側的狀態叫「Hi-Z」,Z 是電路學中「阻抗」(impedance)的符號,也就是說 B 側在這個模式下是「高阻抗」狀態。

我們前面説過,一個輸入腳必須是在高阻抗狀態,它才能接受別人來改變它的狀態,因此當資料的傳輸方向是由 B 到 A 時,B 就應該是高阻抗的狀態(而此時 A 側則是具有驅動能力的輸出狀態);反過來當 DIR 腳是 high 時,傳輸的方向就是由 A 到 B,此時 A 是輸入,也就是高阻抗狀態,而 B 則是輸出。

另外有一隻接腳叫 OE,它是 output enable 的意思。OE 上面有一條線代表它是負邏輯,也就是說 low 的時候它所標示的功能才動作。當 OE 是 low 的時候,74LVC164245 就會以如同上面說明的方式工作;當 OE 是 high 時,不管 DIR 是哪個方向,A 側和 B 側都會進入高阻抗狀態(你可以想像兩邊都是輸入,沒有人輸出,因此訊號不會傳遞到任何一側,這也是為什麼它上面寫「isolation」的原因,因為當 A 和 B 都是輸入時,就等於兩邊的電路斷開來了)。

使用這種方向可切換的邏輯準位轉換 IC 時,有一個很重要的關鍵是「你必須知道現在訊號傳輸的方向,然後控制 DIR 腳,正確改變 IC 的驅動方向」,但實務上有些界面,它的驅動方向可能隨時在改變,而且沒有像 DIR 這樣的訊號可以使用,最常見的例子就是 I2C bus。

I2C 是一種很常用的 bus 系統,bus 上可以同時存在多個 master 與 slave,而且資料的傳輸方向從 master 到 slave 或是從 slave 到 master 都有可能,甚至會在傳輸的過程中突然變化,但 I2C bus 總共只有兩根線:SCL 與 SDA,它並沒有另外的訊號來指示 bus 的傳輸方向(事實上 SDA 和 SCL 是大家共用的,也很難說有什麼方向性),因此這樣的 bus 沒辦法用上面說明的那種邏輯準位轉換 IC 來做轉換。

那我們要如何把一個 3.3 V 的 I2C bus 和一個 5 V 的 I2C bus 接起來呢?

I2C Bus 的邏輯準位轉換

I2C bus 上所有的裝置連接 bus 的界面都是 open–drain,而整個 bus 上則有大家共用的「拉起電阻」,因此任何一個裝置都可以將 bus 拉到 low,而只有當 bus 上沒有人驅動 bus 時,才會靠著拉起電阻讓 bus 恢復成 high 的狀態。

這樣的接法稱之為「wired-OR」,意思就是用線接在一起的「OR」邏輯。在數位電路中的 OR 邏輯就是「多個輸入中只要有一個或一個以上的輸入為 1,輸出就為 1」。在 I2C bus 上則是「整個 bus 上只要有一個或一個以上的裝置驅動 bus 為 low,bus 就為 low。」

這樣的設計讓邏輯 low 比 high 有更高的優先權,也巧妙的解決前面提過的「port conflict」的問題,也因為這樣的 bus 特性,I2C bus 的發明者 NXP 半導體(前身為飛利浦半導體)在很多年前就提出了一個用兩顆 MOSFET 就能對接兩個不同電壓 I2C bus 的方法,相當簡潔、優雅,而且可靠。

這個方法在 NXP 半導體的 AN10441 文件中有詳細的說明,接下來我們簡單地來看一下它:

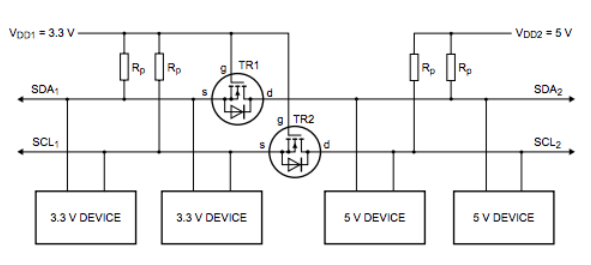

(圖片來源:Bird 提供)

上圖就是用兩顆 MOSFET 連接不同電壓 I2C bus 的方法。左側是電壓較低的 3.3 V 系統,右側是電壓較高的 5 V 系統,電路中的四個 RP 電阻則是兩邊 bus 的拉起電阻,分別將各自的 bus 在沒有裝置驅動時的電壓拉至電源電壓。這個電路有三種狀態:

- 如果兩邊都沒有裝置去拉 bus 的話,因為兩邊都有各自的拉起電阻,3.3 V 側的電壓就會是 3.3 V,5 V 側的電壓就會是 5 V,而圖中的 MOSFET、gate、source 的電壓都是 3.3 V,因此它的 VGS 等於 0,MOSFET 就不會導通;至於 MOSFET 的 body diode,因為是在逆偏壓的狀態下,因此也不會導通,這讓 bus 的兩邊都能被拉到各自的電源電壓,而不會有互相干擾的問題。

- 如果 5 V 側有裝置將 bus 拉到 low,MOSFET 的 body diode 就會變成順偏壓,而開始導通,導通之後,3.3 V 側的電壓會開始下降,當 3.3 V 側的電壓低於某個程度時,由於 MOSFET 的 gate 是接在 3.3 V 電源上,此時 MOSFET 會開始導通,更進一步地讓 5 V 側將 3.3 V 側的 bus 電壓拉低,直到兩邊電壓相等為止;這就是由 5 V 側驅動 3.3 V 側的方法。

- 如果 3.3 V 側有裝置將 bus 拉到 low,由於 MOSFET 的 gate 接在 3.3 V 上,當 source 電壓降低到某個程度,讓 MOSFET 的 VGS 大於它的 threshold 電壓,MOSFET 就會導通,此時 3.3 V 側就會透過 MOSFET 將 5 V 側的 bus 拉低,直到兩邊電壓相等為止;這是由 3.3 V 側驅動 5 V 側的方法。

這個電路用了一個很簡單的方法就讓兩側的 I2C 可以維持同步的邏輯準位,即使它們的電壓可能不同;至於這兩顆 MOSFET 要用什麼樣的零件,一般用途的小信號 N-channel MOSFET 如 BSN20 或 2N7002 這種常用的 MOSFET 都很適用。

小結

這次我們談了利用專用的雙向邏輯準位轉換 IC 來做雙向的準位轉換,另外還介紹了 I2C bus 這種 open-drain、多裝置共享 bus 的邏輯準位轉換方法,希望以上的介紹對讀者們往後設計混合電壓的系統時,有的實際的幫助。

(責任編輯:賴佩萱)

- 【Maker電子學】Flash 記憶體的原理與應用—PART22 - 2025/02/27

- 【Maker電子學】Flash 記憶體的原理與應用—PART21 - 2025/02/21

- 【Maker電子學】Flash 記憶體的原理與應用—PART20 - 2025/01/24

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!