作者:Bird

上一篇文章【Maker電子學】一次搞懂邏輯準位與電壓我們聊了邏輯準位的定義,以及不同準位的系統之間互相連接的問題,這次我們就來實際看看要用什麼樣的電路來讓不同準位的系統之間能互相溝通。

最簡單的情形:從高到低

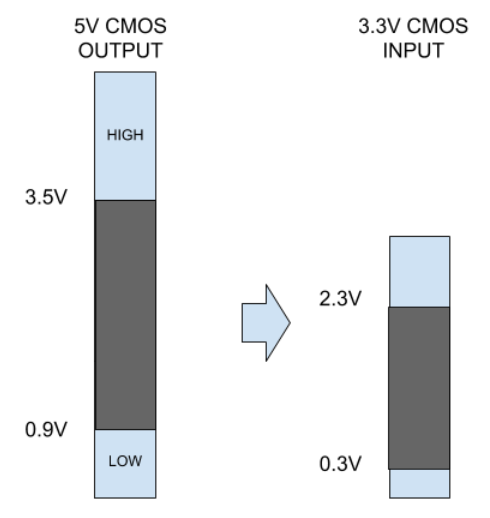

邏輯電壓位準轉換最簡單的場合,就是要用一個高電壓的邏輯準位輸出,去推動一個低電壓的邏輯準位輸入;假設我們要用一個 5 V 的 CMOS 輸出去推動一個 3.3 V 的 CMOS 輸入,相關的邏輯電壓位準標示如下圖所示:

(圖片來源: Bird 提供)

先別管 VOH 對不對得上 VIH、VOL有沒有配上 VIL,首先最重要的一件事就是我們得確定高電壓的一方,它的輸出電壓經過轉換後不能超過低電壓一方的 absolute maximum ratings,不然就會把低電壓這邊的 IC 弄壞。

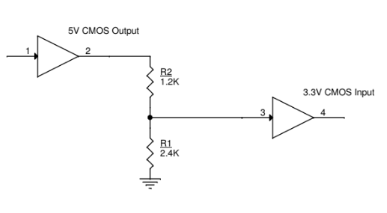

這裡有一個優雅又簡潔的解決方法:分壓電路;我們可以很簡單地用一個兩顆電阻組成的分壓電路,來讓高電壓側的輸出轉換成低電壓側可以接受的電壓範圍。

以 5 V 轉到 3.3 V 來說,我們需要一個 3.3 / 5 = 0.66 倍的電阻分壓電路。看起來像是這個樣子:

(圖片來源: Bird 提供)

根據分壓電路的公式:

VOUT =VIN*(R1 / R1 + R2)

我們取 R1 = 2.4 K,R2 = 1.2 K,可以得到

VOUT=VIN*(2.4 / 3.6)=VIN* 0.6666

因此當 5 V 側輸出最高 5 V 的邏輯準位時,經過分壓電路後得到的電壓就是:

5 V * 0.6666 = 3.333 V

這對 3.3 V 系統來説是個安全的電壓。SAFE!

但邏輯準位的部分呢?我們來看一下 VOH 跟 VIH 的關係;當高電壓側輸出 3.5 V 時,經過分壓電路後的電壓是:

3.5 V * 0.6666 = 2.3331 V

這是最壞的狀況,而即使在最壞的狀況,經過分壓電路後的電壓仍然可以讓低電壓側收到足夠的 VIH,正確地識別邏輯 high 的準位。

設計這種用分壓電路的邏輯準位轉換時,要特別注意「分壓的電阻就是高電壓側的輸出負載」,因此 R1、R2 的總和不能太小,免得高電壓側推不動,但也不能太大,以免容易受到雜訊干擾,典型的設計大概讓高電壓側輸出在 0.1 mA~1 mA 都屬於合理的範圍。

稍微複雜一點的情形:從低到高

如果我們要用一個低電壓準位的邏輯輸出,去驅動一個比較高電壓準位的邏輯電路,就有一點複雜了。

最常見的問題就是我們會需要產生一個足夠高的電壓,以便讓高電壓側的邏輯電路輸入能正確識別邏輯準位 high 的狀態,因為不夠高的邏輯準位電壓會讓高電壓側的邏輯電路進入「你不要玩弄我」的輸入電壓區間,而產生不可預期的動作。

至於邏輯準位 low 的狀態,由於不管是哪種邏輯電路系統,只要不是在吸入電流很大的狀況下,通常都是接近 0 V 的狀態,因此多半沒有問題。

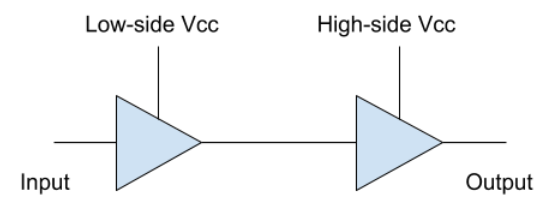

爲了解決這些不同電壓的邏輯電路問題,有許多半導體公司推出了雙電源系統的專用邏輯電壓轉換 IC,這種雙電源的邏輯電壓轉換 IC 内部的結構其實很簡單,如下圖所示:

(圖片來源: Bird 提供)

這種雙電源的邏輯電壓轉換 IC 有獨立的兩組電源系統,因此你可以自由決定低電壓側的邏輯準位、高電壓側的邏輯準位,你可以從 3.3 V 轉 5 V、1.8 V 轉 5 V、1.8 V 轉 5 V,非常的彈性。

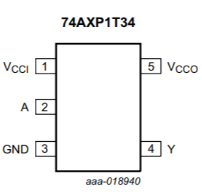

舉個例子來説。NXP 半導體的邏輯 IC 事業部(現為 Nexperia)有一顆 74AXP1T43,就是一種很典型的雙電源邏輯電壓轉換 IC。

(圖片來源: Bird 提供)

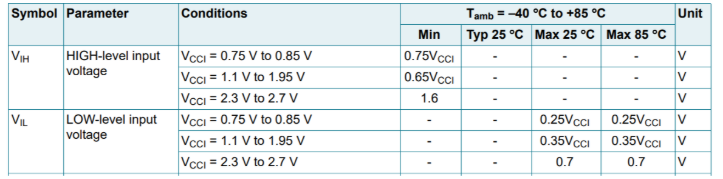

它的 VCCI 接腳是輸入側的電源,可以接受 0.7 V 到 2.5 V 的電源輸入,而 VCCO 接腳則是輸出側的電源,可以接受的範圍是 1.2 V 到 5.5 V,因此 VCCI 算是低電壓側,VCCO 則是高電壓側;接腳 A 是邏輯輸入,接腳 Y 是邏輯輸出,輸出和輸入的邏輯電壓準位則分別由各自的電源電壓決定,這從它的 datasheet 中可以得知:

(圖片來源: Bird 提供)

低電壓側的輸入邏輯準位根據電源電壓範圍的不同,邏輯 high 的門檻大概在 0.7 VCCI 附近,而邏輯 low 的門檻則在 0.3 VCCO 附近,最高不超過 0.7 V。

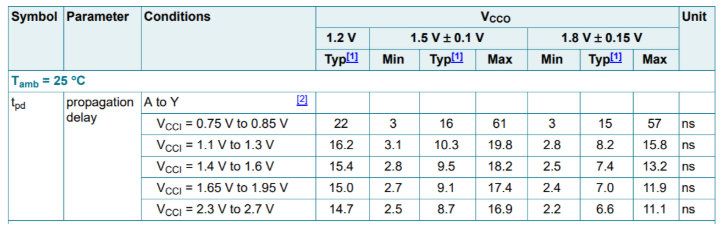

使用這種邏輯電壓轉換 IC 時要特別注意的是它有速度的限制。這個限制來自於 A 接腳收到輸入到 Y 接腳改變輸出狀態之間,會有一點點的時間差,稱之爲「傳輸延遲」(propagation delay),這在 datasheet 上也有清楚地説明:

(圖片來源: Bird 提供)

根據電源電壓的不同,74AXP1T43 的傳輸延遲大概在十多個 ns 到數十 ns 上下,換算成頻率大概都在數十 MHz 以上,因此如果不是用在非常快速的邏輯電路上,一般來說是非常夠用的;知道以上兩種邏輯準位的轉換方法後,你就可以在設計中混用不同的邏輯電壓系統,而不會只受限於單一的邏輯準位。

複合應用實例

今天有一個設計,我們想要用 Arduino UNO 去存取 SD 卡。SD 生來就有可以用 SPI 界面存取的模式,因此我們可以很容易地用 Arduino 上的四支 SPI 訊號(MISO、MOSI、SCK、CS)來和它通訊,但麻煩的是, SD 可以接受的邏輯電壓是 2.7 V~3.6 V,但 Arduino UNO 的邏輯電壓是 5V。

這時我們前面所學的邏輯準位轉換電路就能派上用場了!SPI 的四個訊號中,MOSI、SCK、CS 三者是由 master 送往 slave 的訊號,在這個例子中就是由 Arduino UNO 送往 SD 卡,因此我們需要的是由高電壓邏輯驅動低電壓邏輯的電路,也就是比較簡單的做法:分壓。

而 MISO 是一個由 slave 送往 master 的訊號,因此在這裡它就是由 3.3 V 的 SD 卡送往 5 V 的 Arduino UNO,我們需要一個從低電壓邏輯轉高電壓邏輯的電路。

綜合以上的分析,我們可以設計出這樣的電路:用三個分壓電路處理 5 V 到 3.3 V 邏輯的轉換,再用一顆邏輯準位轉換 IC 處理 3.3 V 到 5 V 邏輯的轉換,就完成了 Arduino UNO 到 SD 卡的界面電路。

另外要特別提一下的是,讀者可能會在某些設計中看到 3.3 V 的 MISO 直接接到 5 V 的 MISO 這樣的做法。根據我們之前的分析,5 V 的邏輯輸入大概要 3.5 V 左右才能「保證」收到邏輯 high 的訊號,但這樣接到底可以不可以?實務上這樣接是會動的,因爲很多 CMOS 邏輯的輸入電路會在輸入超過電源電壓的一半再多一點時,就開始判斷為邏輯 high,但這並不是「保證」的性能(在雜訊比較大或是速度比較快的環境下,這樣接很有可能造成一些不穩定或是不可預期的現象,因此我建議還是乖乖用正規的電路做邏輯準位的轉換比較可靠)。

小結

這次我們談了兩種邏輯準位轉換的方法:從低到高和從高到低,但這兩種方法都是為「單向的界面」所設計的,也就是說它的驅動方向是確定的,不會改變。

那如果遇到雙向的界面該怎麽辦呢?下一回我們再來聊聊雙向界面的邏輯準位轉換。

(責任編輯:賴佩萱)

- 【Maker電子學】Flash 記憶體的原理與應用—PART22 - 2025/02/27

- 【Maker電子學】Flash 記憶體的原理與應用—PART21 - 2025/02/21

- 【Maker電子學】Flash 記憶體的原理與應用—PART20 - 2025/01/24

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!