作者:Bird

前幾次我們聊了 UART 轉換到實體通訊界面 RS-232、RS-422、RS-485,以及這些通訊介面的驅動 IC 應用,這次我們要聊一下這些通訊介面的電氣特性與它們的制定原因,順便也會帶到一些傳輸線的原理。

神秘的終端電阻 #

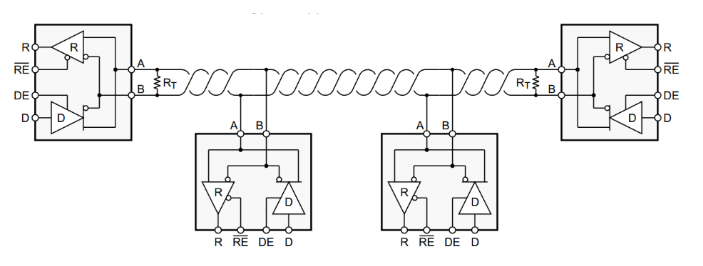

上次我們在解釋 RS-485 的實體網路結構時,看過這張圖:

(圖片來源:Bird 提供)

圖中有兩個神秘的電阻 RT,將 A 和 B 連接起來,我們稱這兩個電阻為「終端電阻」或 terminator,它的目的是在纜線的尾端將訊號消耗掉,避免訊號反射回來。

為什麼訊號會反射,而我們為什麼又怕訊號反射呢?當一個訊號在纜線中傳遞,訊號本身會有一個特性阻抗(characteristic impedance),這個特性阻抗可以想像成訊號本身電壓和電流的比例。

還記得歐姆定律吧?V=IR,或是 R = V/I。如果電壓和電流的比例是純量,那就是電阻;如果是複數,就是阻抗。現在將纜線的尾巴視為一個開路的電路,也就是阻抗無限大的狀況,會發生什麼事呢?開路代表電流流不過去(電流為 0),但隨著訊號而來的電流帶著電荷過來,這些電荷無處可去,該怎麼辦呢?

這時候反射就發生了。這些電荷到達纜線尾巴開路的地方後,因為能量無處可去,只好往回走,因此在阻抗無限大的地方,訊號會原封不動發生全反射,且反射的波形會原來的訊號一模一樣。

如果纜線的尾巴是一個短路的電路,會怎麼樣呢?短路的電路電壓為 0,因此無法消耗能量,訊號中的能量同樣無處可去,所以也會發生反射,只是這次的反射長得不太一樣,訊號的電壓會反過來,正的變負的、負的變正的。

事實上在大部分的狀況中,除了在纜線的尾端會遇到開路或短路外,更常碰到的是在纜線中間阻抗有變化的地方,比方說電路經過連接器、纜線經過駁接等,在這些地方阻抗會發生變化,而訊號通過阻抗變化的地方時,會有一部分的能量發生反射,一部分的能量繼續往前走。

請記得,我們上面講的現象都發生在訊號以接近光速的速度在纜線上傳遞時,雖然傳遞的速度很快,但如果訊號頻率很高,波長相對就會比較短,就有可能在線上面的不同位置有不同的電壓。

比方說,如果我們用 10 Mbps 來跑 RS-485,這個訊號在纜線上的波長就是:λ=v / f = 3108/ 10106= 30(m),如果我們把 RS-485 的纜線拉了超過 30 公尺,就能在纜線上觀察到這個「波」的現象,但如果纜線很短,訊號在纜線上不同位置的差異就不會這麼明顯。

電纜上的波 #

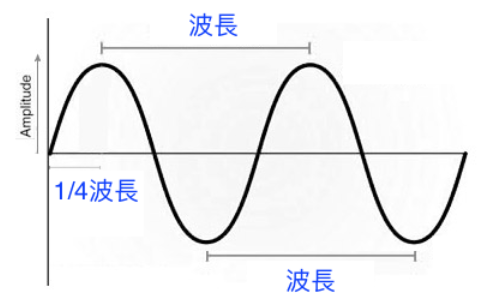

一般來說,有一個原則,就是當纜線的長度超過訊號波長的 1/4 時,就必須考慮這種「波」的效應。

(圖片來源:Bird 提供)

因為以一個週期訊號來說,1/4 波長就是它單邊的振幅從 0 到最大的距離。當訊號在纜線上發生反射時,反射回來的訊號會沿著反方向回到發送端,並沿路和過來的訊號混合,更糟的是,如果反射的訊號回到發送端,而發送端的阻抗和訊號不和,能量便無法消耗掉,訊號便會在發送端再次發生反射,調個頭再繼續它的旅程。

這些反射來反射去的訊號,因為能量用不掉,就會在纜線上來來回回地跑來跑去,而它們疊加在一起的後果,就會產生「訊號變形」,我們來看一個很典型的變形訊號:

(圖片來源:Bird 提供)

這兩個訊號本來應該是方波,但是因為不良的傳輸線設計,導致訊號在線上多處反射,疊加之後的結果,就讓原本應該是方方正正的訊號變成一顆一顆的牙齒,而如果牙齒的凹槽深一點,深到超過輸入端的 VIH或 VIL,就有可能造成接收器的誤動作。

訊號與能量 #

回到 RS-485 上,我們來複習一下 RS-485 的傳送器特性:

- 邏輯 1:VA-VB = +1.5 V ~ +6 V

- 邏輯 0:VA-VB = -1.5 V ~ -6 V

如果傳送器輸出 1.5 V 的電壓差,這個電壓就會流經跨接在 A、B 線之間的兩個終端電阻 RT,另外兩個 120 Ω 的電阻並聯之後是 60 Ω,因此傳送器需要輸出的電壓就是:

V =IR,I = V / R = 1.5 / 60 = 0.025(A)

我們來算算看這傳輸線上的功率:P = IV = 0.025*1.5 = 0.0375(W),也就是說,傳送器總共輸出了 37.5 mW 的功率到整個傳輸線上。

我們再來看 RS-232C 的傳輸線特性。RS-232C 的傳送端電壓規範是:

- 邏輯 0:傳送端+5 V ~ +15 V / 接收端 +3 V ~ +15 V

- 邏輯 1:傳送端 -5 V ~ -15 V / 接收端 -3 V ~ -15 V

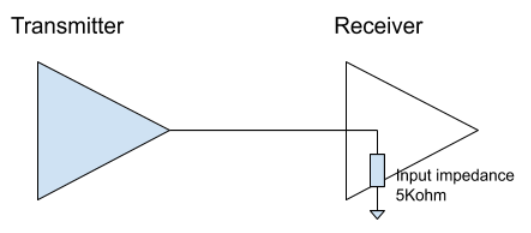

之前我們沒有提過 RS-232C 的終端電阻,因為在 RS-232 的規範中它沒有終端電阻,接收器本身的輸入阻抗就是它的終端電阻。

RS-232C 所規範的最大纜線長度是 50 英呎,差不多是 15 公尺,而 RS-232C 常用的最大 baud rate 是 115200 bps,能造出的最大頻率則是它的一半:57600 Hz。我們來算一下 57600 Hz 在纜線上的波長是多少:λ=v / f = 3*10^8 / 57600 = 5202.2(m)。

哇!這波長居然長達 5 公里多!根據前面提到的四分之一波長原則,RS-232C 的纜線大概不太需要考慮傳輸線上的波效應了,也正由於這個原因,RS-232C 並沒有嚴格規範傳輸線與訊號的特性阻抗。規格中接收器的輸入阻抗允許的範圍是 3 KΩ 到 7 KΩ,一般在設計時會用 5 KΩ 當標準值。

(圖片來源:Bird 提供)

有了電壓和負載,我們就能計算它的驅動電流了:I = V / R = 5 / 5000 = 0.001(A),有沒有發現,RS-232C 線上的電流比 RS-485 要小得多?我們接著計算傳輸線上的功率:P = IV = 0.001*5 = 0.005(W),同樣也比 RS-485 要小得多。

當我們要干擾一個訊號,就必須用比它更強的能量去對抗它,才能改變它的狀態。RS-485 因為線上的功率相對來說比較大,因此跟 RS-232C 比起來確實比較不容易受到干擾,再加上它差動傳輸的特性,如果干擾同時對 A、B 兩根線作用,在接收端也可以將這個干擾消除,種種原因加起來便讓 RS-485 相較於 RS-232C 更耐干擾,能跑更遠的距離。

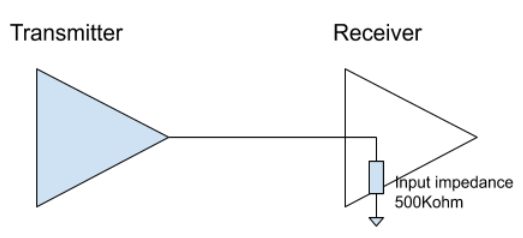

那麼跑在電路板上、電壓準位是 logic level 的 UART,狀況又如何呢?一般邏輯 IC 不一定會特別標明它的輸入阻抗,但是現在 CMOS IC 的輸入阻抗都很高,大概在數百 KΩ 到 1 MΩ 左右。

(圖片來源:Bird 提供)

如果用 500 KΩ、5 V 邏輯準位來計算:I = V / R = 5 / 5000000 = 0.00001(A),當我們用 5 V 的邏輯電壓去驅動一個輸入阻抗高達 500 KΩ 的 IC,流過的電流只有 0.00001 A,而功率也只有:P = IV = 0.000015 = 0.00005(W)

也就是說,在 CMOS IC 之間傳遞訊號所用的功率非常小(這也是 CMOS 電路省電的秘密之一),但如前面所說的,你只要用比它大的訊號就可以干擾它,因此這種高輸入阻抗的訊號傳輸介面是很容易受到干擾的;幸好 UART 訊號通常只跑在電路板上,很少會用纜線連接到比較長的距離,因此需要對抗嚴重干擾的機會其實不大。

小結 #

經由比較 RS-485、RS-232C 以及 UART 訊號的電氣特性,我們發現「訊號如果要耐干擾,傳輸時的功率就要比較大」,而在電壓受限的系統中,要增加傳輸的功率,最好的方法就是「降低接收端的輸入阻抗、增加傳輸的電流」,因此在 RS-485 這種需要跑很遠的系統中,阻抗通常都較低。

訊號跑到目的地後,為了避免能量用不掉而發生反射,需要有終端電阻來將訊號的能量消耗掉。如果訊號發生反射,在傳輸線上來來回回疊加,就會讓訊號變形,甚至破壞訊號;至於要不要認真考慮這些傳輸線的特性,有一個 1/4 波長的原則可以參考:如果傳輸線的長度比訊號的 1/4 波長還長,就需要考慮這些特性。

UART 以及 RS-232C、RS-485 等界面雖然是古老的技術,USB 3 也早已衝上 5 Gbps 甚至更高的速度,但從這些界面設計的規格上,我們仍能學到許多物理原理以及它當初設計時的背後意義。

(責任編輯:賴佩萱)