作者:Bird

上篇文章【Maker電子學】SPI 界面解密—PART 1,我們聊了 SPI 界面的歷史、基本原理、裝置的角色以及它需要用到的訊號,這次我們要來研究一下構成 SPI 核心的邏輯電路與它們在時序上的要求。

移位暫存器 #

移位暫存器是串列通訊介面的核心,它的功能是將並列的資料按照既定的 clock 訊號速度,依序轉換成單一訊號線上的排列狀態。

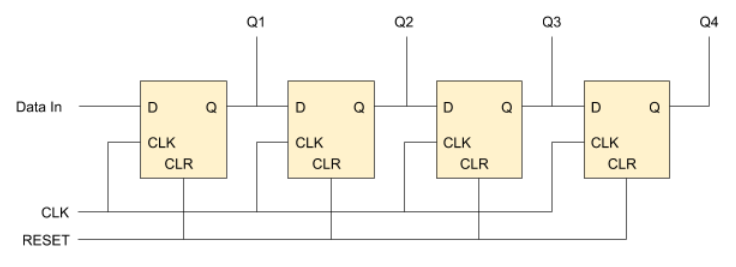

簡化過的 4-bit 移位暫存器電路圖(圖片來源:Bird 提供)

D 型正反器是構成移位暫存器的核心,這種正反器大概是所有的循序邏輯電路中最常使用的,它的動作方式很簡單:在每一次 CLK 的上升緣時,將 D 的狀態反應到 Q,過了 CLK 的上升緣後,Q 的狀態會保持不變,跟 D 再也沒關係。

由於這個動作像是在每一次 CLK 的上升緣將 D 的狀態傳到 Q 後就鎖住不動,因此這樣的正反器電路又被稱爲「栓鎖器」(latch),而每一個 D 型正反器的 Q 輸出都接到下一個 D 型正反器的 D 輸出,如此串接起來後,就構成了移位暫存器;若想把串列資料轉成並列資料,只要把串列資料依序放在 Data In(也就是第一個正反器的 D 輸入上),就能完成轉換了。

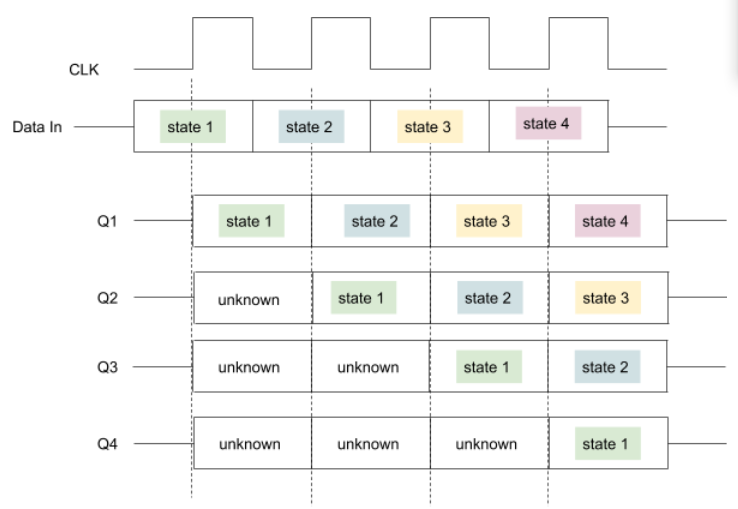

在每一次 CLK 訊號從低變高時,Data In 的狀態會跑到 Q(也就是下一個正反器的輸入上),每經過一次 CLK 訊號的上升緣,前一級 Q 的狀態就會出現在下一級的 Q 上,因此 Data In 上的狀態就會隨著每一次 CLK 訊號的上升,一級一級往後送,下圖是這個 4-bit 移位暫存器經過四次 CLK 訊號變動的時序圖:

(圖片來源:Bird 提供)

經過 4 個 clock 後,Data In 上面在每一個 CLK 訊號上升緣的狀態 state 1、state 2、state 3、state 4 會整整齊齊地出現在 Q1 – Q4 上,也就是說我們已經成功將 4 個 bit 的串列資料轉成並列的資料了。

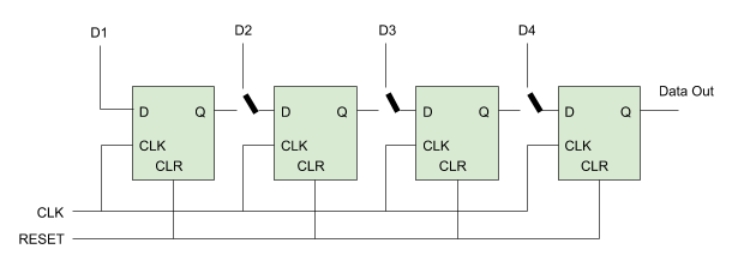

上面說明的是將串列資料轉成並列資料的移位暫存器電路,但如果我們想要把並列資料轉成串列資料呢?其實也是使用相同的 D 型正反器串接起來的移位暫存器電路,不過會需要一些組合邏輯電路的輔助。

我們需要的是一個切換開關,好讓每一級的 D 可以在前一級的 Q 和外部的並列資料輸入接腳 D1-D4 之間切換。當我們要把串列資料送進移位暫存器時,必須先把一級的 D 和 D1-D4 接在一起,然後送一個 CLK 訊號,這時在 CLK 的上升緣,每一級的 Q 就會鎖住它所對應的 D1-D4 狀態。

這時候我們會說「並列資料鎖進移位暫存器」了,接下來將切換開關切到另一個位置,讓每一級的 D 和 Q 連接,當每一次 CLK 的上升緣時,前一級的 Q 就會透過後一級的 D,反應到下一級的 Q,而在最後一級的 Q 上面出現的,就是我們想要的串列資料!

(圖片來源:Bird 提供)

正反器電路只在 CLK 的上升緣那一瞬間會偵測 D 上面的狀態,並將它傳送到 Q,因此當 CLK 在其它時間時,D 上面的狀態其實無關緊要,它是零是 high 是 low 還是不 high 不 low,都不會影響移位暫存器後續輸出資料的正確性。

方波的奧祕 #

所謂「CLK 的上升緣那瞬間」到底是怎麼的一瞬間呢?這就必須把時間的尺度放大來看了。雖然我們畫時序圖時,CLK 看起來好像是個瞬間從 low 變成 high 的方波,但世界上沒有真正的方波,因為時間永遠在動,一個訊號不可能在一瞬間從 low 變成 high,它總需要一點時間來轉變。

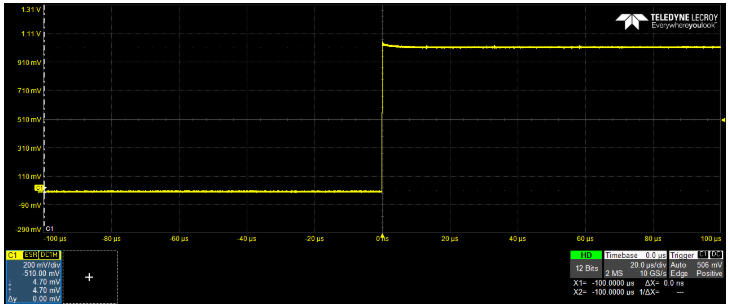

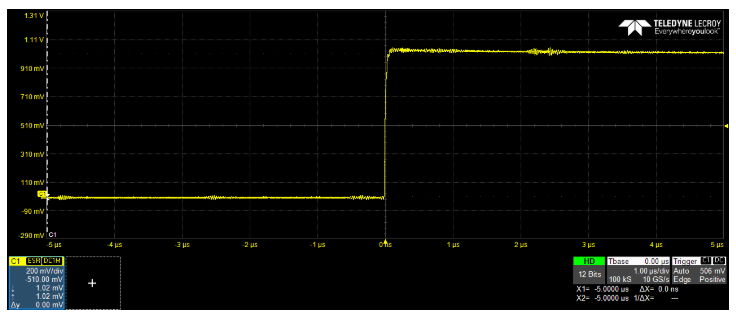

我們在示波器上常常可以看到這樣的方波:

(圖片來源:Bird 提供)

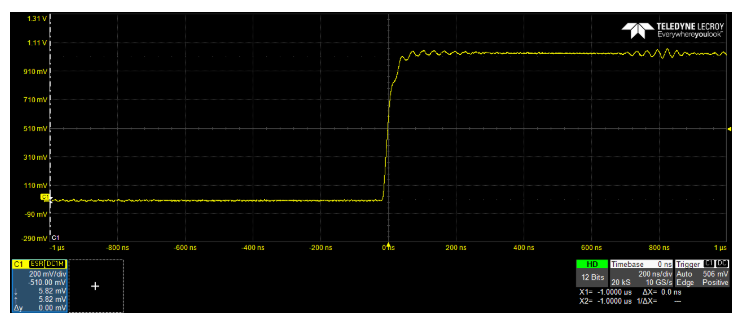

它看起來好像真的就在那麼一瞬間從 low 變成 high,但如果我們把示波器的時間軸拉大一點來看,方波好像就不那麼方了,下面是放大 20 倍後的樣子:

(圖片來源:Bird 提供)

如果放大 100 倍,就會變成:

(圖片來源:Bird 提供)

你還會覺得它很「方」嗎?

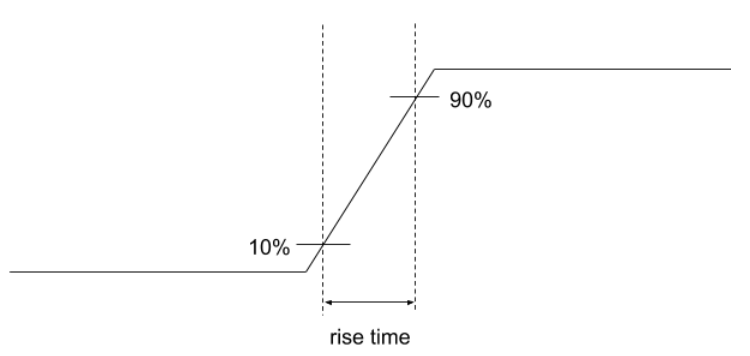

在數位電路的時序分析上,我們會爲這樣看起來很「方」的數位訊號定義一些指標,用來衡量訊號的時間特性。

(圖片來源:Bird 提供)

一個從 low 變成 high 的數位訊號,從它最高電壓的 10% 變成 90% 所需要的時間,稱為這個訊號的「上升時間」(rise time),這個時間可能很短,但絕對不可能是 0,以上面示波器示範的那個訊號來看,它的 rise time 大概在 10 ns 左右,也就是一億分之一秒,是真的很短。

(圖片來源:Bird 提供)

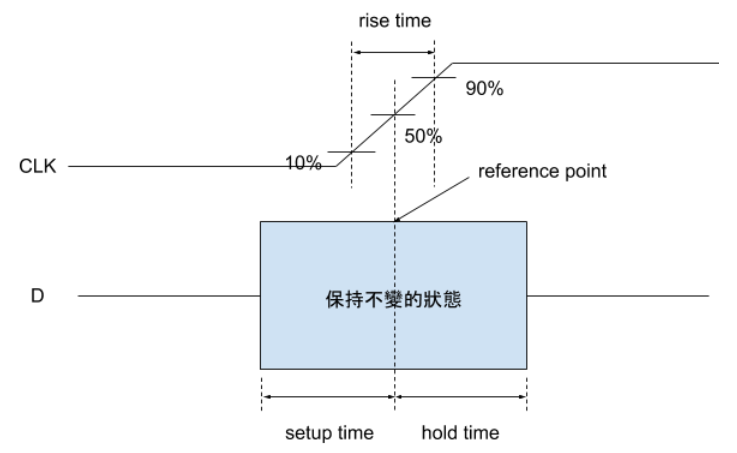

既然 CLK 上升的那一瞬間沒有真的那麼瞬間,正反器偵測到 D 的狀態時,也就不是真的那麼一瞬間(它其實是需要一些時間的)。

當我們用 CLK 訊號的上升緣來偵測 D 訊號的狀態時,我們說 CLK 是這個取樣動作的參考時脈(reference clock);當 CLK 訊號上升到 50% 的那一瞬間,我們稱爲取樣的參考點(reference point),而被取樣的訊號(也就是 D)必須要在這個參考點前後各一小段時間內維持不變,才能確保正反器取樣到正確的狀態。

D 訊號在參考點之前至少要維持不變的時間(稱爲 setup time);在參考點之後至少要維持不變的時間(稱爲 hold time),這兩個名詞在 IC 的規格書或時序圖上,常會用 TSU 和 TH 來代表,而 rise time 則常用 Tr 來代表,那當然有上升就會有下降,因此從 90% 降到 10% 的時間,稱爲 fall time,常用 Tf 來代表。

SPI 之所以可以用數 MHz 甚至數十 MHz 的速度運作,是因爲它有一個 clock 訊號用來作爲資料取樣的參考(還記得嗎?UART 沒有 clock 訊號,它的資料取樣點是接收端自己決定的),而這個 clock 訊號以及它和 data 訊號之間的關係,在時序上有非常嚴謹的定義和要求,因此在設計電路時,只要符合這些定義和要求,便能確保資料在高速傳輸下的正確性。

小結 #

這次我們很認真的研究了 SPI 的核心—移位暫存器的工作原理以及它在時序上的定義和要求,下一次我們再繼續來探討 SPI 實際上有哪些訊號和這些訊號的功能。

(責任編輯:賴佩萱)