作者:Bird

上一回我們說明了 Non-Volatile Memory 的發展過程:從單次可寫入的 PROM,到可利用紫外線抹除再寫入的 EPROM,再到可以利用電子方法抹除再寫入的 EEPROM。

這一回我們會繼續說明 EEPROM 的原理,與 Flash Memory 的發展。

EEPROM #

EEPROM 是可以用電子方式抹除的 EPROM,也就是說要抹除 EEPROM 的內容時,只要施加適當的電子訊號就可以,不必使用紫外線照著之類的方法。

事實上 EEPROM 的結構和原理都與 EPROM 極為接近,它同樣利用一個完全絕緣的浮動閘極來保存電荷、利用電子穿隧效應來讓電子注入或離開浮動閘極。我們來看一下 EEPROM 的寫入與抹除是怎麼操作的。

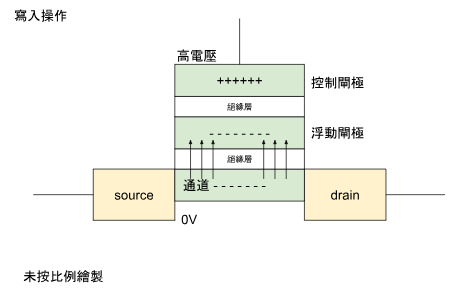

寫入時,我們要讓電子進入浮動閘極,於是我們在控制閘極上加上很高的電壓,並讓 source-drain 的通道開啟,而且維持在 0V 左右。

(圖片來源:Bird 提供)

由於控制閘極上的高電壓,控制閘極與通道之間會形成一個強大的電場,讓通道中的電子有能力藉由量子力學中的電子穿隧效應,穿過浮動閘極與通道之間的絕緣層,進入浮動閘極。當這個電場消失後,已經進入浮動閘極的電子就會被困在裡面,因為浮動閘極的周圍都是絕緣層,沒有任何的線路與它連接,所以浮動閘極裡的電子沒地方跑,會乖乖地待在裡面數年甚至數十年之久。

而當浮動閘極中有電子存在時,這些電子所形成的電場會干擾控制閘極對通道的控制能力,因此讀取時,我們會在控制閘極上加上一個沒那麼高的電壓,只要足以讓通道開啟就好;如果這時控浮動極中有電荷,它就會干擾控制閘極的電場,進而讓通道無法開啟;如果這是浮動閘極中沒有電荷,控制閘極就可以正常地讓通道開啟。

從另一個角度來看,浮動閘極會影響這個電晶體的 Vth,也就是控制閘極要讓電晶體的通道開啟時所需要的電壓,又叫 threshold voltage。

既然可以利用穿隧效應讓電子進入浮動閘極,那為什麼不同樣利用穿隧效應讓電子也可以離開浮動閘極呢?於是 EEPROM 就這樣誕生了。

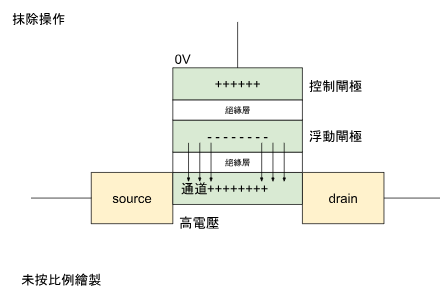

(圖片來源:Bird 提供)

抹除時,我們要讓電子離開浮動閘極。這次我們讓控制閘極的電壓維持在 0V 左右,而在通道這一側加上高電壓,讓電場的方向與寫入時反過來;受到通道這一側的強大電場影響,浮動閘極中的電子藉由電子穿隧效應越過通道與浮動閘極中的絕緣層,進入通道被中合掉,於是浮動閘極中的電子就被清除了。

與 EPROM 不同的地方是,要讓浮動閘極中的電子可以反往通道離開,需要一層非常非常薄的絕緣層。1978 年 Intel 推出第一顆 16Kbit 的 EEPROM 2816 時,它的二氧化矽絕緣層厚度只有 200 Å ,也就是 20 奈米,這在當時算是相當困難的製程。

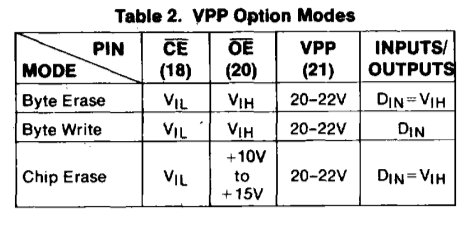

而 EEPROM 在寫入和抹除時用來產生強大電場的高電壓則必須在寫入和抹除時額外提供。下圖是從當年的 2816 EEPROM datasheet 中截圖出來的規格:

(圖片來源:Bird 提供)

可以看到,在寫入時,VPP 接腳上需要施加高達 20-22 V 的電壓。

由於 EEPROM 在重複燒寫時通常不用從電路板上拆下來,因此系統中會需要能產生燒錄高壓的電路,對設計來說相對比較麻煩,於是 Intel 隨後又推出了 2816 的下一代 2816A,並在晶片上內建了升壓電路,可以直接利用 5 V 電源在晶片內部產生 20-22 V 的燒錄電壓,免去了外部升壓電路的麻煩。

要在晶片上製作升壓電路,一般都會使用 charge pump 的結構,而不太可能使用 boost converter 電路,因為 boost converter 需要一個電感當作儲能元件,但在晶片上要製作電感相對來說比較困難,也不容易做出 charge pump 所需要的感值,而在晶片上要製作電容器則相對容易,因此只要搭配電晶體切換電路,就可以利用電容器的並聯充電、串聯放電,把電壓倍增,在晶片上做出升壓電路。

如今我們使用的各種 EEPROM 或 flash 記憶體晶片,很少聽到會需要額外供應特殊的電源才能燒錄,都是因為晶片上已經內建 charge pump 的升壓電路。

並列控制介面 #

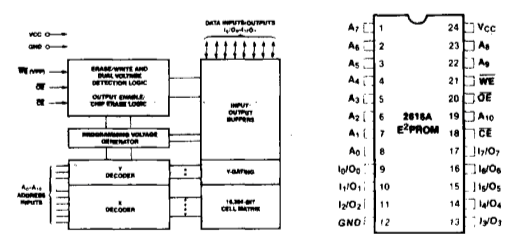

像 Intel 2816 這種 EEPROM,使用的是與早期 EPROM 相容的並列式控制介面(parallel interface)。

(圖片來源:Bird 提供)

從接腳圖中可以看到,2816 有專用的位址和資料接腳,以及用來控制資料存取的 CE/OE/WE 等訊號。

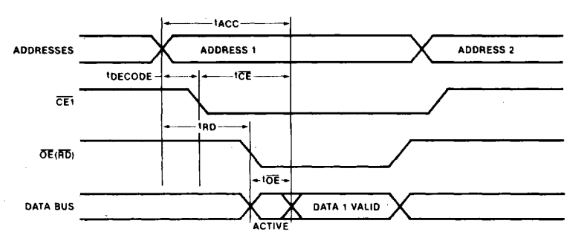

(圖片來源:Bird 提供)

上圖是一個典型的並列式介面存取 EEPROM 的時序圖。首先 CPU 或是任何要讀取 EEPROM 的裝置,要先把位址訊號準備好,然後將 CE(chip enable)訊號拉低,讓 EEPROM 晶片知道要開始工作了,這時 EEPROM 會把位址訊號讀進去解碼、選擇對應的儲存單元,將內容讀出來準備好在輸出緩衝電路上,接著 CPU 就可以把 OE(output enable)訊號拉低,讓資料出現在資料接腳上。

大家有沒有發現,以上這些讀取動作,都沒有時脈訊號?對,這種早期的記憶體介面,由於速度慢,其實不太需要 clock 訊號。

以上圖的時脈為例,2816 的 tACC 是 200 ns,也就是說從位址訊號準備好到資料可以讀出來,需要 200 ns,換算成時脈的話大概是 5 MHz,以今天的 CPU 速度來說,這個存取時間幾乎是不可思議地慢,也難怪它不需要 clock 訊號來確定位址與資料線的取樣時間。

這種不需要 clock 訊號的邏輯電路,叫做非同步(asynchronous)邏輯。由於沒有 clock 訊號,資料到底在什麼時刻被取樣其實沒有很確定的 timing,一般只能用在速度很低的介面。

當速度越來越快,我們就會需要 clock 訊號來讓介面可以有一致的時間參考基準。關於有 clock 訊號的同步式(synchonous)介面,我們在後面介紹 flash memory 的高速介面時會再探討。

小結 #

這一回我們介紹了 EEPROM 的詳細運作原理:如何利用電位差控制量子穿隧效應,讓電子進入或離開浮動閘極,以做到寫入或抹除,同時我們也簡單說明了 EEPROM 的並列式控制介面,以及它與現今的同步式介面有什麼不同。

下一回我們會開始介紹 Flash Memory 快閃記憶體。

(責任編輯:賴佩萱)