作者:Bird

前幾回我們介紹了 I2C EEPROM 的運作原理和使用方法,這一回開始我們要進入 SPI flash 記憶體的世界了。

Flash 介面的分類 #

我們在介紹 flash 記憶體的歷史時,曾經介紹過 flash 分成 NOR flash 和 NAND flash 兩種。前者較早發明、密度較低、儲存資料相當可靠;後者稍晚發明、密度較高,但儲存資料的能力較不穩定。

早期的 flash 記憶體多半使用並列式的介面,有獨立的資料、位址接腳,以及一些用來控制鎖定、讀寫模式的訊號。在 NOR flash 陣營,有個叫做 CFI(common flash interface)的標準,它定義了 NOR flash 的介面和指令標準,而在 NAND flash 陣營,則有一個叫做 ONFI(Open NAND Flash Interface)的標準,定義了類似的東西,不過由於 NAND flash 先天上資料比較容易錯,使用起來需要更多的資料錯誤檢查和校正等管理,因此它的的介面和指令更爲複雜。

除了並列介面外,串列介面也逐漸出現在 flash 記憶體上。串列介面所需要的訊號數量少、IC 的封裝也比較小,在許多應用裡會比並列式的 flash 介面更爲適合,而這其中,又以 SPI 介面最爲適合。因爲 NOR flash 動輒數十到數百 Mb,而 NAND flash 更是單顆已經到 Gb 等級,這個量級的容量如果用我們上一回介紹 EEPROM 的 I2C 介面來傳輸,可能燒錄一顆 1 Gb 的 NAND flash 要超過 24 小時,因此在短距離可以跑到數十甚至上百 MHz 的 SPI 介面就成了更合理的選擇。

這一回,就讓我們先從 SPI 介面的 NOR flash 開始介紹。

SPI NOR Flash #

SPI NOR flash 現在很常用在各種 SoC 的啟動 firmware 儲存,比方說很常用的 ESP32-S2 module ESP32-S3-WROOM 裡面就用了一顆 4 MB 到 16 MB 不等的 SPI NOR flash,用來儲存程式碼和資料。

我們就以 Winbond 的 W25Q32JV 這顆 32 Mbit 的 SPI NOR flash 為範例,來介紹 SPI NOR flash 的使用方法吧。

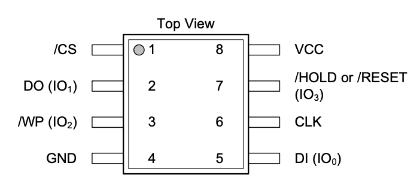

SPI NOR flash 有個很大的優點就是接腳數量少。大部分的 SPI NOR flash,不管容量大小,都是 8 隻腳的包裝。

(圖片來源:Bird 提供)

扣掉電源和 ground 兩隻腳,其實只有六隻腳用來傳輸訊號,而因為 SPI 介面的簡潔,這六隻腳就能以每秒十幾 M bytes 甚至 數十 M bytes 的速度傳輸資料。

SPI 介面 #

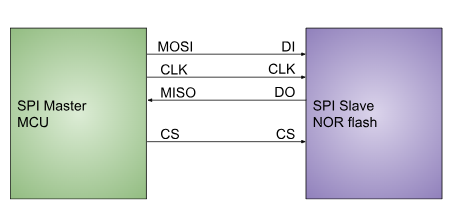

典型的 SPI 介面只有 4 個訊號:DI、DO、CLK、CS。在使用 SPI 控制 flash 的情境中,MCU 是 SPI master,負責產生 clock、送出指令,而 SPI flash 則是 slave,被動的接受 clock、接受指令。

(圖片來源:Bird 提供)

由於 SPI 介面不像 I2C 介面有個組織來統一制定標準(它最早是從 Motorola 的 6800 系列微處理器上衍生出來的),因此訊號命名在不同產品上常常不一致。從 master 送往 slave 的資料訊號叫 MOSI(master out,slave in),但在某些 slave 晶片上回叫做 DI(data in),而從 slave 送往 master 的資料訊號叫 MISO(master in,slave out),但在某些 slave 晶片上叫做 DO(data out)。另外兩個訊號則是負責用來鎖定資料的 clock,以及選擇 slave 晶片的 CS。

SPI 介面其實很單純,它就是利用在 master 和 slave 兩端的移位暫存器,將多個 bit 的訊號依序載在 MOSI 或 MISO 上傳輸,至於要傳送什麼、資料的格式等,都是由系統設計的協定來定義,與 SPI 介面無關。

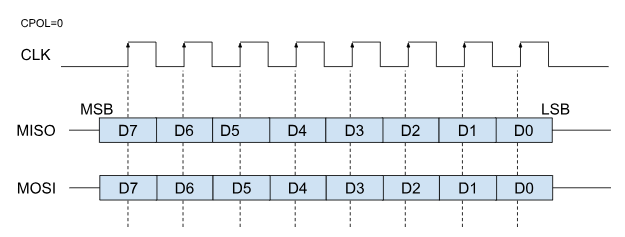

SPI 所有的資料傳輸都以 8-bit(1 個 byte)為單位(可能是因為它誕生在 8-bit 微處理器那個年代),但一個傳輸週期中可以包含不止一個 byte,它可以是兩個 bytes(16-bit)、三個 bytes(24-bit)甚至更多,而且一般的慣例是,在一個 byte 裡面的 MSB 先傳,LSB 最後。

(圖片來源:Bird 提供)

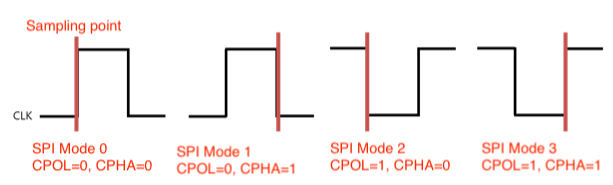

在 SPI 的歷史上曾經出現過一些訊號時脈的變化組合。它用兩個分別稱之為 CPOL 和 CPHA 的狀態位元來表示,一個代表 clock 的極性(polarity),另一個代表 clock 的相位(phase)。這兩個狀態位元總共有四種組合。不過這樣的設計來自於當年的 SPI 只用很簡單的移位暫存器來實作,它會利用 clock 訊號的其中一個 edge(上升或下降)來鎖定資料、另一個 edge(下降或上升)來移動移位暫存器裡的資料。

(圖片來源:Bird 提供)

因為總共有四種組合,慣例上會將它們命名為 mode 0 – 3,用以決定 SPI 通訊時,clock 跟 data 之間的相對關係。

根據 datasheet 上的說明,W25Q32JV 會在每次 CS 訊號拉低時,開始一次 SPI 通訊,接著在每一次 clock 訊號的 rising edge,都會讀入一個 bit 的訊號,每 8 個 clock 為一個單位,讀入一個 byte。

送指令 #

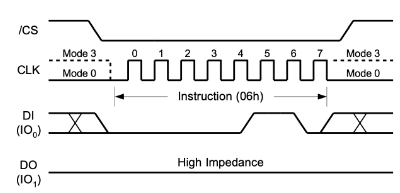

(圖片來源:Bird 提供)

上圖是 W25Q32JV 送一個單位元指令 0x06 的時序圖,可以看到在 master 把 CS 拉低後,就接連送出 clock 訊號,而 W25Q32JV 會在每一個 clock 的 rising edge 去取樣 DI,拿到每一個 bit 的狀態。由於 SPI 是 MSB 先送,而我們畫時序圖的時候右邊是現在、左邊是過去,時間是從右向左流動,像示波器一樣,因此當我們把 8 個 bit 的波形畫在時序圖上時,它就會按照我們熟悉的二進位系統排列順序出現。

以上圖來說,8 個 clock 對應到的 8 個 bit 狀態就是從左到右的 00000110,換算十六進位就是 0x06。

從上圖我們也可以發現,W25Q32JV 根本不在意 SPI 是 mode 0 還是 mode 3,也就是說它不在意 clock 訊號在 idle 時到底是 low 還是 high,反正它就是在 CS 變成 low 之後,開始等待 clock 訊號的每一個 rising edge,讀取資料。

讀取指令 #

我們來看一個在 SPI NOR flash 上最簡單的指令:讀取。

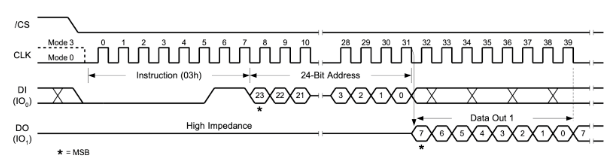

(圖片來源:Bird 提供)

W25Q32JV 的讀取指令是 0x03;在 SPI 上對 flash 晶片送出 0x03 這個數字之後,接著還要送出 3 個 bytes 的讀取位址。由於 W25Q32JV 有 32 Mbit 的容量,也就是 4M bytes,它的定址範圍是 0 – 4194303,用十六進位表示就是 0x3FFFFF,因此要定址 4 MB,會需要 3 個 bytes 的位址資料;在送完指令之後,master 會需要接著送出 3 個 bytes 的讀取位址,一樣是 MSB 先送。

到這裡,我們總共送出了 8 + 24 = 32 個 clock,也就是 4 個 bytes 的資料。

接著呢,master 會繼續送出 clock 訊號,這時 W25Q32JV 就會在接下來的每一個 clock 的 falling 變化 DO 腳的狀態,並且讓 master 在 rising edge 讀取 DO 的狀態,,而接下來的這 8 個 clock,就是剛剛 master 送進去的那個位址所儲存的資料。

於是,我們就用了 8 + 24 + 8 = 40 個 clock,讀到了 1 個 byte 的資料。

W25Q32JV 可以接受最快的 SPI clock 是 133MHz,如果讀取一個 byte 需要 40 個 clock,那麼這樣讀取的最大速度就會是

133,000,000 / 40 = 3,325,000(bytes / sec)

大概是一秒 3M bytes,其實相當快了。

但如果我們在它讀完一個 byte 之後,繼續送出 clock,會發生什麼事呢?聰明的讀者一定猜得到,就像 I2C EEPROM 的 page read 一樣,W25Q32JV 會繼續送出下一個位址的內容,如此一直下去。

因此如果是連續讀取的話,W25Q32JV 的讀取速度會變成

133,000,000 / = 16,625,000(bytes / sec)

大概是一秒 16M bytes。

因此我們知道,受限於需要用 3 個 bytes 傳送目標位址,SPI NOR flash 的隨即讀取速度會比連續讀取要慢很多。

小結 #

這一回我們介紹了 SPI NOR flash 所使用的 SPI 介面,並說明了 SPI 介面的時序,以及讀取 flash 內容的指令長什麼樣子。

下一回我們會繼續介紹 SPI NOR flash 的結構,以及其它重要的指令。

(責任編輯:賴佩萱)