作者:Bird

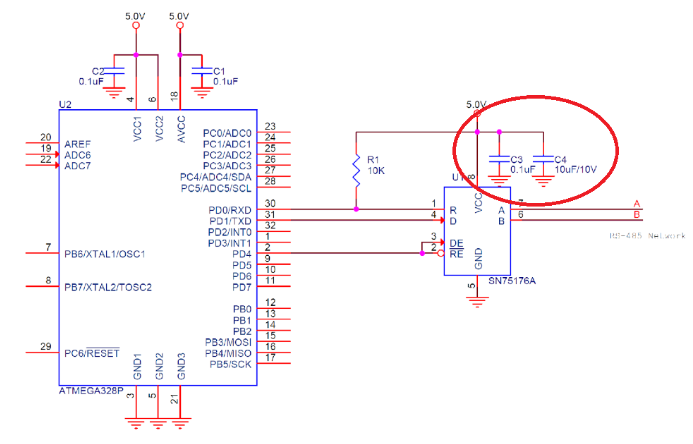

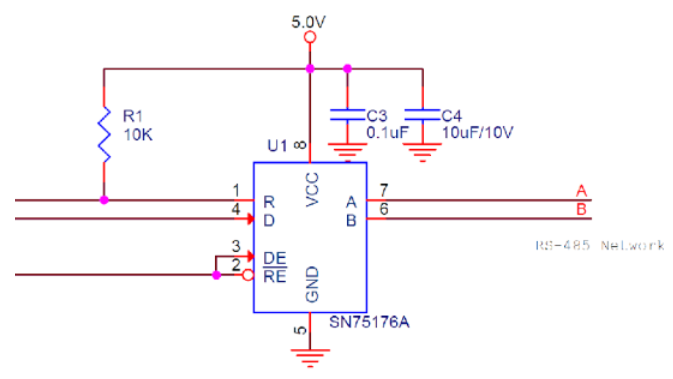

在認識 UART 界面系列文章中介紹 RS-485 的某一篇中,我曾經畫過一個 RS-485 收發界面的示範電路。在那個電路中,RS-485 的收發器 IC SN75176A 的電源上並聯了兩個電容器:一個 0.1 uF 的,以及一個 10 uF 的電容器。

(圖片來源:Bird 提供)

這個電路引來蠻多迴響,有不止一位讀者問到爲什麼要放兩個電容器,因此這一回我們就從這個電路開始,來聊一下電源系統的濾波設計。

濾波電容器 #

我們在介紹電源電路的系列文章中有提到,現在大部分的電源電路都是有回授的穩壓電源:電源電路會持續監控它自己的輸出電壓,藉此調控它的輸出,讓輸出的電壓維持在一個穩定的範圍。

既然電源本身已經是穩壓的了,爲什麼電路設計上還會有各式各樣的濾波電容器或是其它的濾波電路,散佈在各處的電源電路上?

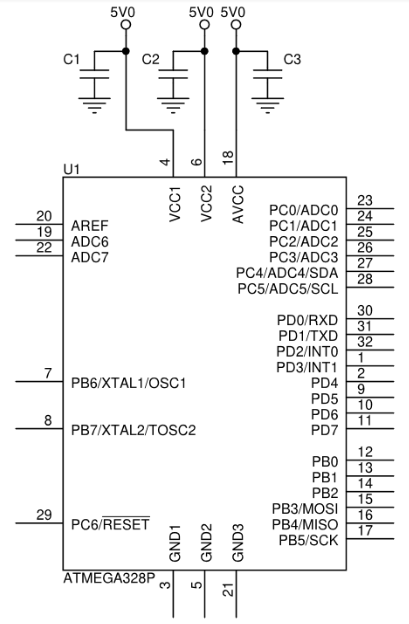

讓我們舉一個很常見的例子。Arduino Uno 所使用的 MCU ATmega328p 有三支電源接腳:VCC1、VCC2、AVCC。在一些比較講究的電路設計中,它的電源濾波會畫成這樣:

(圖片來源:Bird 提供)

雖然三隻腳都是由 5 V0 這個電源供電,但在畫圖時會把他們分開,並各自畫上自己的濾波電容器。

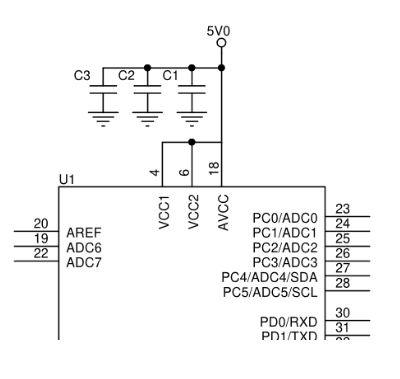

如果畫圖的人比較不講究,也可以畫成這樣:

(圖片來源:Bird 提供)

上面兩個電路圖是完全等效的,它們所產生的 netlist 是完全一樣的,而這樣設計的原意是我們希望 VCC1、VCC2、AVCC 每一支腳都要有一顆自己的濾波電容,而且在 layout 時要儘量將每一顆濾波電容放在靠近接腳的地方,但由於上面兩張電路圖會產生完全一樣的 netlist,進到 PCB layout 軟體時,如果 layout 的工程師完全只依賴 netlist,他不見得會知道電路設計的人希望每一支腳都要有一顆自己的濾波電容,而有可能將三顆電容擺在一起。

我們先來看看爲什麼要這樣設計。

無所不在的寄生特性 #

在畫電路時,將兩個點一條線連接起來時,我們就稱這兩個點在同一個「net」上。在電路圖的世界中,所有的連接線都是理想的連接線:電阻爲 0、net 上各點沒有電位差、沒有相位差…

但現實世界往往並不是這麼美好的。理想的連接線並不存在,就算我們有電阻爲 0 的超導體,訊號在電路上傳遞仍然需要時間,在頻率夠高時線上各點仍然會有相位差… 等。

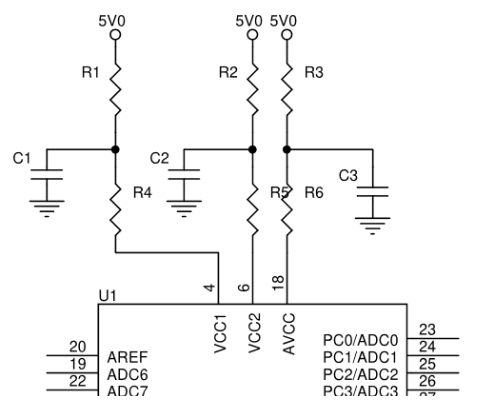

以電源電路來說,電源電路的輸出走到 IC 的電源電路這一段線路,它或多或少會有一點點的寄生電阻,因此實際上的電路會變成這樣:

(圖片來源:Bird 提供)

R1 和 R4 就是從電源 IC 到 VCC1 接腳這段連接線上的寄生電阻,它會跟 PCB 上走線的長度、寬度、銅箔厚度等因素有關。

我們知道 MCU 的耗電是會隨著程式的執行而變動的,當 MCU 裡的 CPU 很忙時,或是周邊裝置動作很多時,耗電會增加;而當 CPU 很閒,或是周邊裝置沒什麼在動作時,耗電就會降低。

假設來自電源 IC 的供電電壓是準確的 5.000 V,且 R1 和 R4 加起來是 0.01 ohm。如果此時 VCC1 接腳的耗電量是 15 mA,根據歐姆定律,在 R1 和 R4 上會有壓降:

V = I * R = 0.015(A)* 0.01(Ω)= 0.00015 V = 0.15 mV

這時 VCC1 接腳上的電壓就不是精確的 5.000 V 了,而是 5.000 – 0.00015 = 4.99985(V)

這一點點的電壓對 VCC1 來說似乎不痛不癢,一般數系統的電源輸入主要是提供能量,因此對於電壓波動的容忍範圍相對來說比較大。但對於 analog 的電源輸入如 AVCC 接腳來說,事情就不太一樣了。

Amega328p 裡面有個 ADC,可以用來測量電壓並將之轉換成數字,ADC 在做轉換時需要一個參考電壓 Vref,用來決定測量的範圍。ATmega328p 的 Vref 可以用暫存器選擇一個內部的 1.1 V band gap 電壓、AREF 接腳、或是 AVCC 電源電壓。

ATmega328p 的 ADC 是 10-bit 的,如果我們用 5 V 的 AVCC 當作參考電壓,它的每一個 LSB 代表的電壓刻度就是:

5 / 2^10 = 5 / 1023 = 0.00489 V = 4.89 mV

因此當 AVCC 上的電壓變化超過 4.89 mV 時,就會對 ADC 的輸出產生至少 1 個 bit 的變化,影響 ADC 的測量精度。

我們前面算過,當耗電是 15 mA、線路上的電阻是 0.01 ohm 時,會有 0.15 mV 的壓降,這時的電壓變化相對於 ADC 一個 bit 的電壓來說仍然很小,不會影響測量,但如果線路上的電阻變成 1 ohm,在同樣的耗電下壓降就會變爲 15 mV,這時就會對 ADC 的測量結果產生影響。

爲了避免這個現象發生,一般的設計原則就是要讓電源線路上的電阻儘量減小,也就是讓上圖中的 R1+R4,或是 R3+R6 儘量小,但有時候事與願違,如果板子很大、電源 IC 遠在天邊,就得走一條很長的線路才能抵達被供電的接腳,又因爲走線密度的關係沒辦法走太粗的線路,R1 就是小不了,該怎麼辦呢?

這時加上一個小小的濾波電容器 C1,就可以幫我們解決這個問題。使用濾波電容時,我們希望它的放置位置儘可能地靠近被供電的接腳,讓 R4 儘量減小,這時 R1 與 C1 就會構成一個 RC 濾波器。

假設 R1 是 0.1 ohm,當 VCC1 上的電流在 1 mA 跟 15 mA 之間變化時,R1 上的壓降會在 0.1 mV 跟 1.5 mV 之間變化,因此 VCC1 的電壓就會在 4.999 V 跟 4.9985 V 之間變化,而當 VCC1 上的電壓變化時,C1 裡的電荷有助於「減緩」這個變化。比方說當 VCC1 上的電流開始增大時,因爲 R1 上的壓降增加,來自 R1 的電壓就會降低,但此時 C1 裡因爲仍有電荷,C1 裡的電荷就會流向 VCC1,維持 VCC1 上的電壓。

事實上 C1 的電壓仍然會隨著裡面電荷的減少而降低,但 Q1 的存在會「減緩」VCC1 上的電壓變化。如果 VCC1 上的耗電電流一直都是恆定的,來自 R1 的壓降也都會是恆定的,這時整個系統就會進入一個穩定的平衡狀態。

因此這裡必須要再次強調,電源上的濾波電路都是爲了應付「變動」而存在的,不管是負載的變動還是電源的變動。

那麼 C1 要放多大,才足以應付 VCC1 上的電流變化呢?

根據電容器的電流公式:I = C(dV/dt)。電容器上的電流正比於電壓對時間的變化率,而這個斜率就是電容器的大小。當電流不變時,電容值越大,電壓的變化率就越小,因此我們可以知道,C1 放得越大,VCC1 上的電壓變化就會越小,反過來說,如果 VCC1 上吃的電流很大,C1 就要放得比較大,讓電壓的變化維持在較小的範圍。

一般我們在設計數位電路時,大部分的場合下,單顆 IC 或是單支電源接腳放 0.1 uF 的陶瓷電容作爲電源濾波就很足夠了但是在某些狀況下,如果 IC 的耗電較大,0.1 uF 的陶瓷電容可能不足以供應穩定電源接腳電壓所需的電荷量,這時候就會放 1 uF、4.7 uF 甚至更大的濾波電容器。

寬頻濾波電路 #

以我們最前面提到的那個電路爲例:

(圖片來源:Bird 提供)

SN75176A 是 RS-485 的驅動 IC,由於 RS-485 是相對來說阻抗偏低的通訊標準,它的驅動電流較大,因此驅動 IC 所需要消耗的電流也會比較大。SN75176A 最大可以輸出 60 mA 的驅動電流,因此我在設計這個電路時就放了比較大的 10 uF 濾波電容。

但爲什麼放了 10 uF 的濾波電容,還要另外並聯 0.1 uF 的電容呢?這也是許多讀者問到的問題。

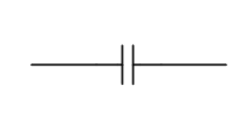

它的理由和前面的濾波電路設計一樣:世界上沒有東西是完美的,電容器也一樣。現實世界中所有的電容器都不可能是完美的電容器,我們在電路中畫的電容器符號是這樣:

(圖片來源:Bird 提供)

而電容器的阻抗是這樣:XC = 1 / 2𝝅fC

這是理想的電容器阻抗:它的阻抗隨著頻率的上升而越來越小(因爲頻率項 f 在分母),因此電容器對高頻訊號的導通較好,對低頻訊號的導通較差,而對頻率爲 0 的直流訊號則有無限大的阻抗。

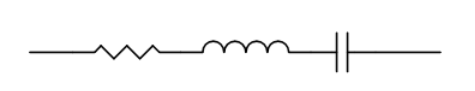

但是現實世界中的電容器其實長這樣:

(圖片來源:Bird 提供)

除了電容器本身外,還會有與它串聯在一起的寄生電感和寄生電阻,這個寄生電阻和電感又叫做等效串聯電阻 ESR(equivalent series resistance)和等效串聯電感 ESL(equivalent series inductance)。ESR 會限制電容器的充放電電流,而 ESL 則會在訊號的頻率增高時冒出來攪局。

電感的阻抗公式是這樣:XL =2𝝅fL

也就是說,電感的阻抗與訊號的頻率成正比,訊號頻率越高,電感的阻抗越大。電感傾向讓頻率低的訊號通過,而阻擋頻率高的訊號,和電容器正好相反。

由於 ESL 是和電容器本人串聯在一起的,它們的等效阻抗會相加。當訊號的頻率越來越高,電容器的阻抗會越來越小,但是 ESL 的阻抗會越來越大,而由於容抗的公式頻率是在分母項,它下降的速度是 y=a/x 的雙曲線;感抗上升的速度則是 y = ax 的直線,下降的速度追不上上升的速度,因此在某個頻率以上,ESL 造成的感抗會開始大於電容本身的容抗,讓整個元件的阻抗開始上升。

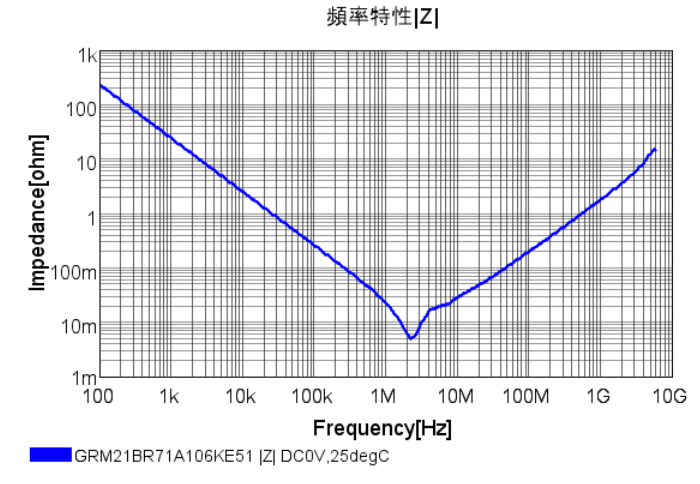

我們來看看陶瓷電容大廠 Murata 的 datasheet:

(圖片來源:Bird 提供)

以 GRM21BR71A106KE51 這顆 10uF 的陶瓷電容爲例,它的 datasheet 中有列出它的阻抗與頻率的關係。從圖中可以看出,大概在頻率 1.2 MHz 以上時,它的阻抗就開始隨著頻率上升,因此它對 1.2 MHz 以上雜訊的濾波能力就會比較差。

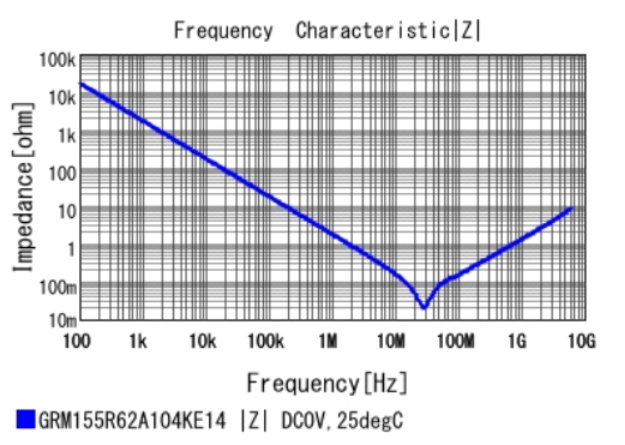

讓我們來看另外一顆 0.1 uF 電容的頻率特性圖:

(圖片來源:Bird 提供)

從圖中可以看出來,這顆編號 GRM155R62A104KE14 的 0.1 uF 陶瓷電容,阻抗的最低點落在頻率 12 MHz 附近,當頻率超過 12 MHz 以上時它的阻抗才開始增加。

由於陶瓷電容先天上結構的關係,容量越大的陶瓷電容,它的 ESL 會越大,阻抗開始反轉的頻率也會越低,而大容量的陶瓷電容在低頻的特性阻抗會比小容量的陶瓷電容要大(因爲 C 項在阻抗公式的分母),因此大容量陶瓷電容對低頻訊號的濾波效果會比較好。

如果我們將 0.1 uF 和 10 uF 的電容器並聯在一起,它們兩者的特性阻抗也就會並聯在一起,低頻的訊號大部分會經由 10 uF 的電容被旁路掉,而高頻的訊號則會走 0.1 uF 的路徑被旁路掉,一網打盡,沒有遺漏。

因此在很講究濾波頻寬的場合,我們常常會設計很多顆不同容量的電容器並聯在一起,達成所謂的「寬頻濾波」效果,讓所有頻率的雜訊都能有良好的導通路徑被旁路掉。

小結 #

這一回我們從一個 RS-485 收發界面的示範電路開始,探討了電源濾波電路的設計,並說明了「世界上沒有完美的理想零件和電路」這個很重要的概念。所有的濾波電路、各種補償性的設計,都是爲了對抗真實世界中零件的不完美特性。最後爲了解答許多讀者的問題,我們也說明了那個示範電路中,爲什麼要並聯 0.1 uF 和 10 uF 兩個電容器的理由。

希望這一期的文章能讓大家對電源電路的濾波設計有更深一層的了解,能更深入的知道電子零件各種與理論不相符的不完美特性,並且知道如何去克服這些問題。