作者:Bird

上一回【Maker電子學】Flash 記憶體的原理與應用—PART5(NAND Flash),我們說明了 NAND Flash 的電路結構,以及它為什麼可以擁有高於 NOR Flash 甚多的密度。

這一回我們要繼續探討,NAND Flash 這樣的結構有什麼弱點、代價以及要如何克服這些問題。

NAND Flash 的讀取

(圖片來源:Bird 提供)

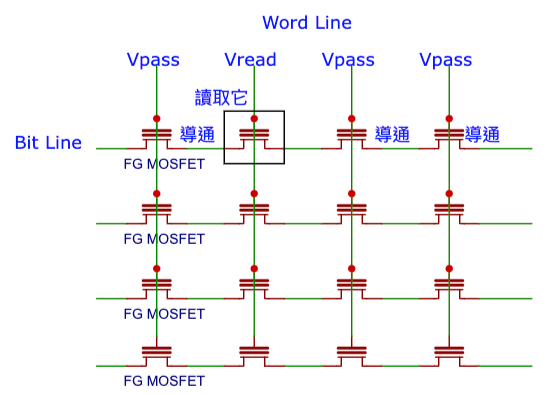

我們在上一回介紹過,NAND Flash 在結構上會有許多不同 word 的同一個 bit 串聯在一起;要讀取時,我們會在要讀取的 word line,也就是對應的 gate 上,加上一個叫 Vread 的電壓,然後在同一串的 bit line 的其它 gate 上,加上一個叫 Vpass 的電壓。

Flash 的每一個 bit 都是一個具有浮動閘極(floating gate)的 MOSFET,而浮動閘極裡有沒電荷,則決定了這顆 MOSFET 的臨界電壓 Vth。當這個 bit 被抹除成為 1 後,它的浮動閘極裡沒有電荷,這時候這顆 MOSFET 的臨界電壓會小於 0 V,而當這個 bit 被寫入成為 0 之後,它的浮動閘極裡就有被困的電荷,因為這些電荷會干擾控制閘極所產生的電場,使得它的臨界電壓上升。

這時它的臨界電壓就會大於 0V,我們可以利用這個特性來讀取這個 bit 的狀態:在要讀取的 bit 它的 gate 上加一個 0 V 左右的電壓,如果這個 bit 是 1,它的 Vth 就會小於 0 V,而加上 0 V 就足以使它導通;如果這個 bit 是 0,它的 Vth 就會大於 0 V,於是 0 V 就不足以使它導通,這個 0V 就稱之為 Vread;而 Vpass 則是一個可以讓 bit cell 裡的 MOFSET,不管浮動閘極裡有沒有電荷,都可以導通的電壓,,為了要讓其它的 MOSFET 都導通,這個 Vpass 要大於所有 MOSFET 的 Vth,一般來說 Vpass 都在 4-5V 左右。

於是,在一整串串連起來的 MOSFET 中,我們對於要讀取的 bit 加上 Vread,而對於其它 bit 加上 Vpass。這時整個串聯電路導通與否,取決於被加上 Vread 的那顆 MOFSET 的 Vth 是大於還是小於 Vread;如果它的 Vth 大於 Vread,那麽 Vread 就無法使它導通,這時整串 MOSFET 就不導通;如果它的 Vth 小於 Vread,那麽 Vread 就可以使它導通,這時整串 MOSFET 就會導通,我們可以藉由測量電流來知道整串 MOSFET 有沒有導通,進而知道要讀取的那個 bit 的狀態。

讀取干擾

Flash 的 bit 要被寫入時,其實是在它的 gate 上加上一個相對來說很高的電壓,讓電子藉由場致發射所引起的穿隧效應進入浮動閘極。由於場致發射需要一個相對很強的電場,寫入時加在 gate 上的電壓會高達 18-20 V,這個電壓會在 flash 的晶片上使用 charge pump 之類的電路產生。

當我們要讀取一個 bit 時,同一串電路上的其它 MOSFET 都會利用 Vpass 讓它們進入導通狀態。這個 Vread 雖然沒有像寫入時的 gate 電壓那麼高,但其實也會引起微量的穿隧效應,使微量的電子進入這些 MOSFET 的浮動閘極;重複進行讀取操作後,會使得這些被 Vpass 蹂躪過的 MOSFET 它們的 Vth 往正向移動,如果這個 bit 本來是 1,它的 Vth 很低,但因為重複讀取使它的 Vth 變高超過臨界值 0V,這時 bit 就會變成 0,導致資料錯誤。

這個現象叫做讀取干擾(read disturb),它在重複讀取時會變得很明顯,不過讀取干擾只會破壞資料的內容,不會破壞 cell 的結構,只要重新擦除 bit 的內容再寫入,資料就可以恢復正常。

溫度的影響

MOSFET 的 Vth 會受溫度變化影響。當溫度上升,Vth 會降低;反之如果溫度降低,Vth 則會上升,其變化的幅度大概在 -1.5mV/°C 左右,因此從室溫 25°C 上升到 70°C時,Vth 會降低 70mV 左右,使得讀取時的 margin 減小。

因此 flash 晶片在設計上都會需要偵測溫度,並隨著溫度來改變讀取時的 Vth 電壓。

區塊讀取

由於每次讀取都會造成大量的讀取干擾,NAND Flash 跟 NOR Flash 比較起來,相對沒有那麼穩定與可靠,因此 NAND Flash 在晶片層級的設計上多半會引入錯誤檢查、錯誤校正等機制,也就是利用額外的容量來儲存部分的 redunent 資訊,藉以修正一定程度的錯誤,這個機制叫做 ECC – error checking and correction。

絕大多數的 ECC 演算法都是以區塊為單位來計算,因此 NAND Flash 需要讀取一整個區塊、進行 ECC 的計算與校正後,才能把資料往外送,所以絕大多數的 NAND Flash 都將介面設計成一次讀取一個 block 的形式,而 block 的大小則在 512 bytes 到 1K bytes 不等。

這也就是為什麼我們常常聽到「NAND Flash 不能隨機存取,因此不能直接在它上面執行程式」的原因,有些 NAND Flash 的介面設計讓它可以逐個 byte 定址,則是在晶片上利用一塊緩衝區暫存整個 block 的資料,達到逐個 byte 讀取的功能。

小結

這一回我們說明了 NAND Flash 讀取干擾(read dusturb)的形成原因,以及它對資料可能造成的影響。我們也說明了為什麼 NAND Flash 一般都只能整個區塊整個區塊的讀取。

下一回我們要開始進入實際的應用,來看看各種 Flash 的晶片要如何操作。

(責任編輯:賴佩萱)

- 【Maker電子學】Flash 記憶體的原理與應用—PART22 - 2025/02/27

- 【Maker電子學】Flash 記憶體的原理與應用—PART21 - 2025/02/21

- 【Maker電子學】Flash 記憶體的原理與應用—PART20 - 2025/01/24

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!