作者:Bird

上一回我們講了 NOR Flash Memory 發明的故事,以及在 Flash Memory 這個產業中至關重要的關鍵人物舛岡富士雄,也提到他與 Toshiba 的恩怨情仇。舛岡富士雄隨後也發明了現在更廣泛使用、密度更高的 NAND Flash。

不過,這一回我們要先來看看 NOR Flash 的結構與技術。

隨機存取記憶體 RAM

在 EEPROM 與 NOR Flash 剛發明的那個年代,另外一種記憶體—DRAM(dynamic RAM)也正蓬勃發展(DRAM 發明之前的主要記憶體技術是利用拴鎖(latch)電路構成的 SRAM(static RAM))。

SRAM 由於可以靠邏輯電路正反器的特性保持狀態,當它裡面一個 bit 被設定爲 0 或 1 時,只要電源持續存在,就可以保持這個狀態,不會改變,因此稱之爲「靜態」(static)的隨機存器記憶體(RAM),但構成一個正反器需要至少四個電晶體,再加上讀取和定址所需要的電路,SRAM 的一個 bit 至少需要 6 個電晶體,因此它的密度始終無法提高。

而 DRAM 則是利用電容器裡面的電荷來儲存狀態,每一個 bit 由一個電容器來代表內容,電容器裡的電荷有無就代表那個 bit 的值。但由於半導體製程的限制,晶片上的電容器容量無法做太大,絕緣也無法做太好,因此裡面的電荷會隨著時間而漸漸流失。爲了對抗這種現象,DRAM 在使用時需要定期「刷新」(refresh),利用刷新電路根據電容器裡原來的電荷狀態去幫它補充電荷。不同晶片所需要的刷新速度不一樣,DRAM 製造商都會告訴你該如何使用它。由於 DRAM 在使用時需要一直刷新,就算沒在存取它時也一樣,因此被稱爲「動態」(dynamic)的隨機存取記憶體。

一般 DRAM 裡的電容器可以保存資料的時間大概在數十到一百 ms 左右,換句話說你必須在它裡面的電荷消失之前就 refresh 一次。這麼短的時間聽起來好像很瞎,它的記憶力也太短了,怎麼能稱得上是記憶體,但即使對於 80 年代平均 clock 速度在幾 MHz 的微處理器來說,就算是 50 ms 也相當於 50000 個 clock cycle,其實已經是很長很長的時間了。時隔多年,對於現在動輒上 GHz 的處理器速度來說,能儲存資料幾十個 ms 已經像是一輩子那麼長了,因此 DRAM 仍然有它的實用性。

DRAM 的結構

DRAM 最大的優點是它的密度。DRAM 裡的一個 bit 只需要一個電容器加上一個讀取及寫入用的電晶體。

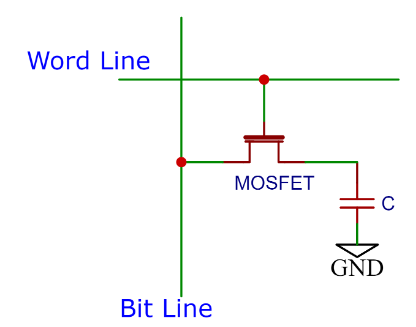

DRAM 的 bit 結構 (圖片來源:Bird 提供)

要讀取或寫入 bit 時,就用 word line 打開電晶體,這時 bit line 就會透過導通的 MOSFET 跟電容器相連。如果是讀取,就用電壓感測電路感應 MOSFET 上的電壓,就可以知道電容裡有沒有電荷,決定 bit 的狀態;如果是寫入,就可以透過 MOSFET 對電容器充電或放電,改變電容器裡的電荷狀態。

只要把這個電路照著 word line 和 bit line 的方向延伸,就可以變成一個記憶體陣列。

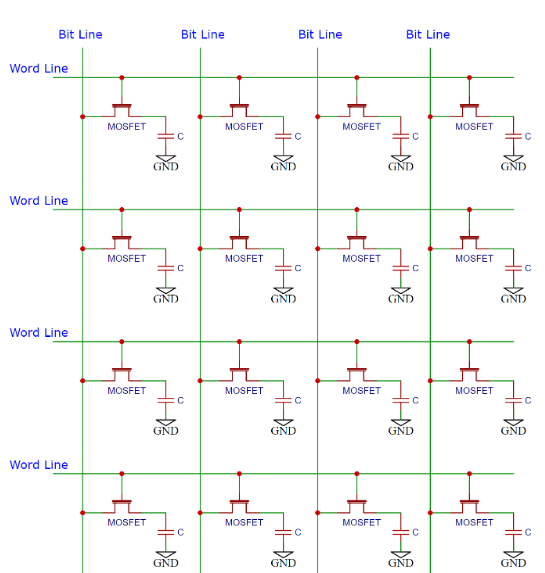

(圖片來源:Bird 提供)

上圖就是一個 4-bit x 4 的 DRAM 陣列。在存取的時候,word line 一次只能打開一條,才能正確存取到對應的 bit,至於要打開哪一條 word line,則會有另外的位址解碼(address decoder)電路負責。

那麼 NOR Flash 的結構呢?

NOR Flash 的結構

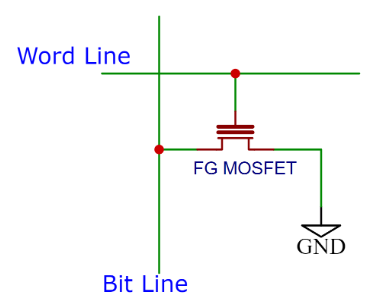

NOR Flash 的 bit 結構甚至比 DRAM 還要簡單。這是典型的 NOR Flash 單一 bit 的電路:

NOR Flash 的 bit 結構 (圖片來源:Bird 提供)

由於 Flash 是靠 MOSFET 中浮動柵極內的電荷狀態來記憶資訊,MOSFET 本身就是記錄資訊的裝置,因此它沒有 DRAM 的電容器,整個 bit 就只有一顆電晶體,而且這顆電晶體就是具有浮動柵極的 MOSFET。圖中的 MOSFET 符號,多了一條橫線,代表的就是與任何電路都不相連、完全絕緣的浮動柵極(floating gate)。

要讀取 bit 的內容時,只要用 word line 打開對應的 MOSFET,再感測 bit line 上的狀態就好了。如果浮柵極中沒有電荷,word line 上加在柵極的電壓就可以正確控制 MOSFET 打開,讓 bit line 與 MOSFET 另一端的 GND 導通;如果浮動柵極中有儲存電荷,它就會干擾柵極的電場,讓柵極無法控制 MOSFET 的導通,而讓 bit line 無法感應到 MOSFET 另一端的 GND。

藉由感測這個 MOSFET 能否被 word line 正確控制,我們就可以知道浮動柵極中有沒有儲存電荷,進而知道這個 bit 的狀態。

由於相較於 DRAM 少了一顆電容器(而且 DRAM 中的那顆電容器佔晶片面積還不小),flash 的密度先天上就比 DRAM 要高。舛岡富士雄在研發 NOR flash 的時候,Toshiba 也正在積極發展 DRAM 的技術,而且由於兩者結構上的相似性,舛岡博士可以借用當時的 DRAM 製程來改善 Flash 的製程,可以說是一個完美的巧合。

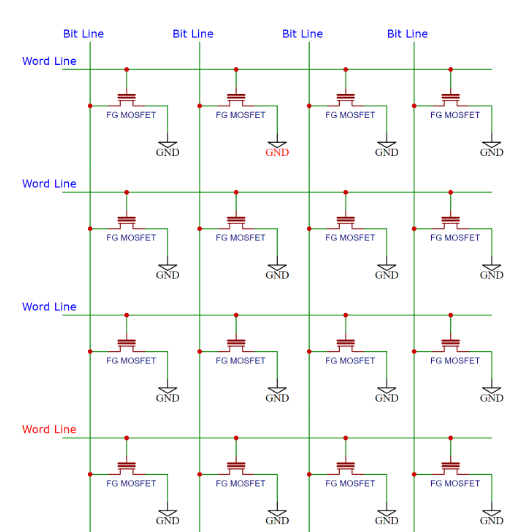

我們將 NOR Flash 的 bit 電路延伸成一個記憶體陣列:

(圖片來源:Bird 提供)

這是一個 4-bit x 4 的 Flash 電路,可以看到它跟 DRAM 電路高度的相似性。

由於 NOR Flash 電路的每一個 bit 都是跟相鄰 word 的同一個 bit 連接在一起,這個結構與邏輯閘的 NOR gate 電路極爲相似。

NOR gate 電路(圖片來源:Bird 提供)

因此在 NAND Flash 發明之後,這種傳統結構的 Flash 電路就被成爲 NOR Flash。

小結

這一回我們介紹了在 EEPROM 和 Flash Memory 剛發明的那個年代,也同樣蓬勃發展的記憶體 DRAM 的技術,以及與 DRAM 高度相似的 NOR Flash 記憶體結構。

下一回我們要來看看另一個 Flash 記憶體的結構:NAND Flash,以及它爲什麼可以將 Flash Memory 的密度再度提高到另一個境界。

(責任編輯:賴佩萱)

- 【Maker電子學】Flash 記憶體的原理與應用—PART22 - 2025/02/27

- 【Maker電子學】Flash 記憶體的原理與應用—PART21 - 2025/02/21

- 【Maker電子學】Flash 記憶體的原理與應用—PART20 - 2025/01/24

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!