正在崛起的Edge AI應用特別需要著重低功耗、小體積與安全性等方面表現的技術解決方案,已經在嵌入式/物聯網(IoT)裝置扮演核心角色的微控制器(MCU)、微處理器(MPU)自然成為首選,目前市面上最新方案在我們先前的報導中也有一些詳細的介紹;而在MCU/MPU之外,屬於可程式化元件的FPGA或許也是開發Edge AI時可以考慮的選擇。

早在20年前,原本被用來作為產品原型開發的FPGA,就常被視為「威脅」ASIC市場地位的電子裝置核心元件替代方案,特別是在針對新興應用少量多樣、變化速度快的設計中,因為其容易更改邏輯功能的特性,會是比全客製化ASIC更具效益的選項。

隨著時間更迭,FPGA技術陣容也持續演進、擴大,除了運算性能媲美一般高階處理器SoC的產品之外,也有功耗表現不遜於MCU的「小」型方案;無論是消費性電子、車用、工業等市場領域,FPGA都穩穩佔據一席之地。

隨著AI無所不在的新時代來臨,FPGA也再一次展現其「戰略價值」,各家供應商在不同的應用領域各擅勝場──例如在高性能運算市場,Intel (在2015年收購FPGA供應商Altera)與Xilinx (在2020年被AMD收歸旗下)積極攻佔正在大規模資料中心扮演要角的智慧網卡(Smart NIC)應用,以提供可編程彈性的優勢與其他網通SoC業者分庭抗禮。

而在邊緣端,包括Microchip (在2018年收購Microsemi,而Microsemi在2010收購專精FPGA技術的Actel)、Lattice、QuickLogic等業者,都有針對Edge AI相關應用的解決方案。

什麼樣的Edge AI應用適合選擇FPGA?

如Microchip嵌入式解決方案工程師林于凱(Mark Lin)在該公司的一場線上研討會所介紹,以一般嵌入式應用而言,MCU/MPU在架構上具備相當高的靈活度,也有容易上手的開發平台能使用C語言等高階語言來進行編程與除錯等設計流程,但可能無法針對特定應用進行特殊的調整來提升所需性能,相較之下FPGA與ASIC在這方面能有更好的最佳化表現。

他進一步指出,雖然MCU/MPU通常能提供更高浮點運算速度、單位成本與功耗也會比FPGA來得低,相較之下FPGA具備更低延遲、可靈活配置I/O、支援平行處理、可重複編程、可快速上市等特性,在一些需要較高運算力的Edge AI應用中特別能發揮優勢。

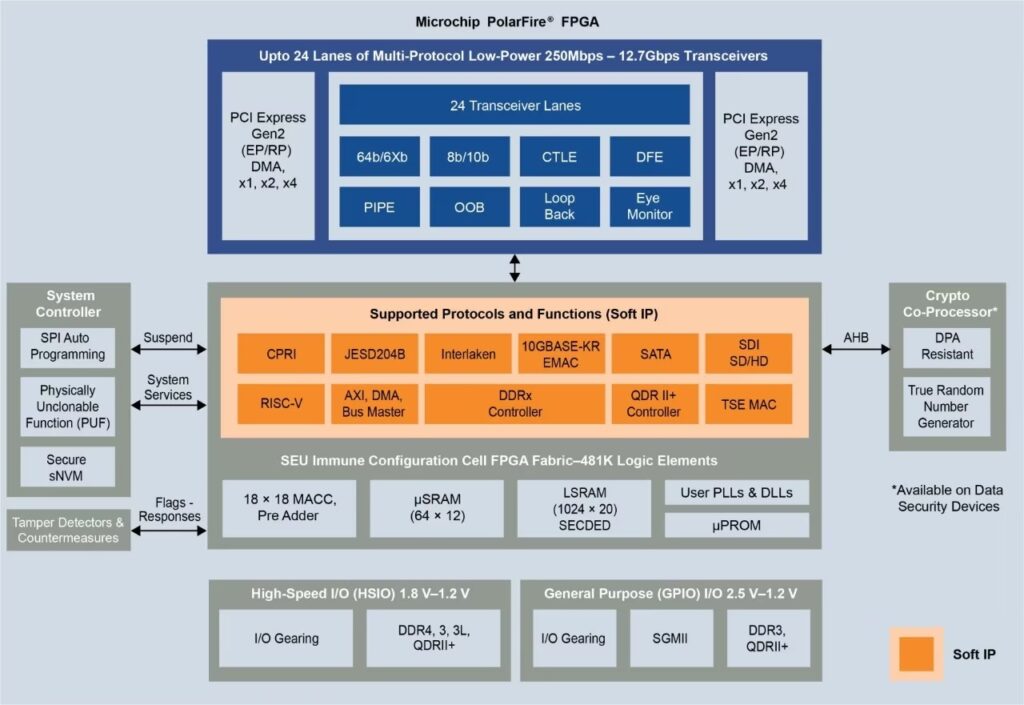

典型的FPGA元件內部包括分別由查找表(LUTs)與正反器(Flip-flop)組成的組合邏輯與循序邏輯區塊(最高達500K units),一些乘法器單元、SRAM/快閃記憶體、PLL/DLL電路、高速I/O與收發器(最高達24 lanes),以及其他周邊電路,如下圖以Microchip的PolarFire系列(原始開發者為Actel)低功耗FPGA為例的架構。

PolarFire FPGA元件架構。(圖片來源:Microchip)

不過Mark強調,如果是針對特定功能需求完全客製化的應用,ASIC仍在邏輯密度以及單位成本上具備高於FPGA的優勢,但前提是要有足夠大量的訂單。

Microchip將自家FPGA的目標市場定位在「智慧嵌入式視覺」(Smart Embedded Vision,SEV)平台,涵蓋像是工業用機器視覺、虛擬/擴增實境(VR/AR)頭戴式裝置、先進駕駛輔助系統(ADAS)、無人機視覺、安全監控、視訊廣播設備、醫療影像、手持式熱像儀等應用。

定位在中階FPGA的PolarFire系列內含100K~500K邏輯單元(Logic Elements,LEs),可支援4K高解析度影像,訴求小佔位面積(11 x 11 mm)、高可靠度、高安全性等優勢,號稱整體功耗較同級產品低30%~50%,並因為具備豐富的記憶體(DDR4、LPDDR3)與I/O連結介面(12.7G SERDES、1.6 Gbps LVDS、PCIe Gen2x4)等資源,整體成本也更低。

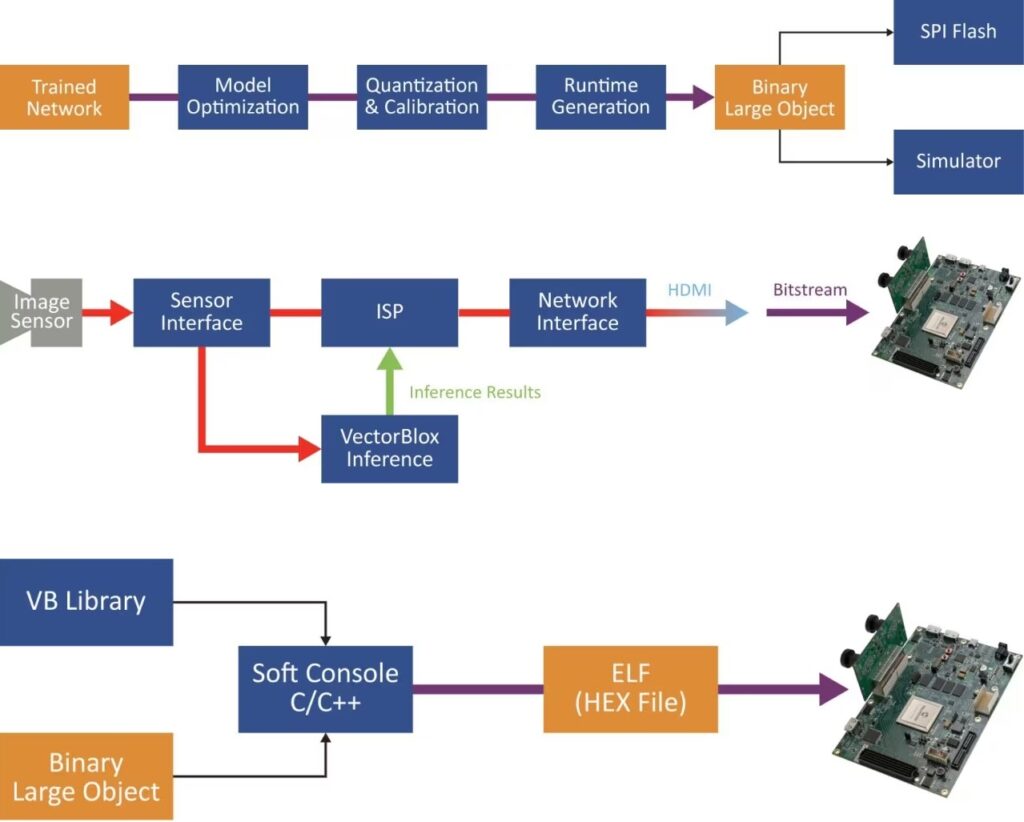

在Edge AI開發工具的支援上,Microchip提供名為VectorBlox的軟體開發套件(Accelerator SDK),能協助開發者以簡單的三個開發步驟利用PolarFire部署AI推論應用。該SDK是以OpenVINO平台為基礎的前端工具,支援TensorFlow、Caffe、MxNet、PyTorch與DarkNet等常見ML框架,號稱不需要具備FPGA專業知識就能快速進行評估,並透過以軟體覆蓋的實作方式,更新CNN時不需要重新編程FPGA。

Microchip的Edge AI三步驟開發流程:1. 模型最佳化;2. 完成硬體配置;3. 編寫嵌入式程式碼。(圖片來源:Microchip)

VectorBlox支援模型最佳化、量化、校準、Runtime生成等工具,能將來自TensorFlow或ONNX框架的神經網路描述編譯為二進位大型物件(BLOB)儲存在快閃記憶體中,在執行時導入DDR記憶體。該SDK還包括名為CoreVectorBlox的加速器IP,由矩陣處理器(MXP)和MXP CNN IP組成,在需要共享神經網路工作負載時可以實例化為單核心或多核心加速器。

低功耗、開發平台的支援為市場競爭重點

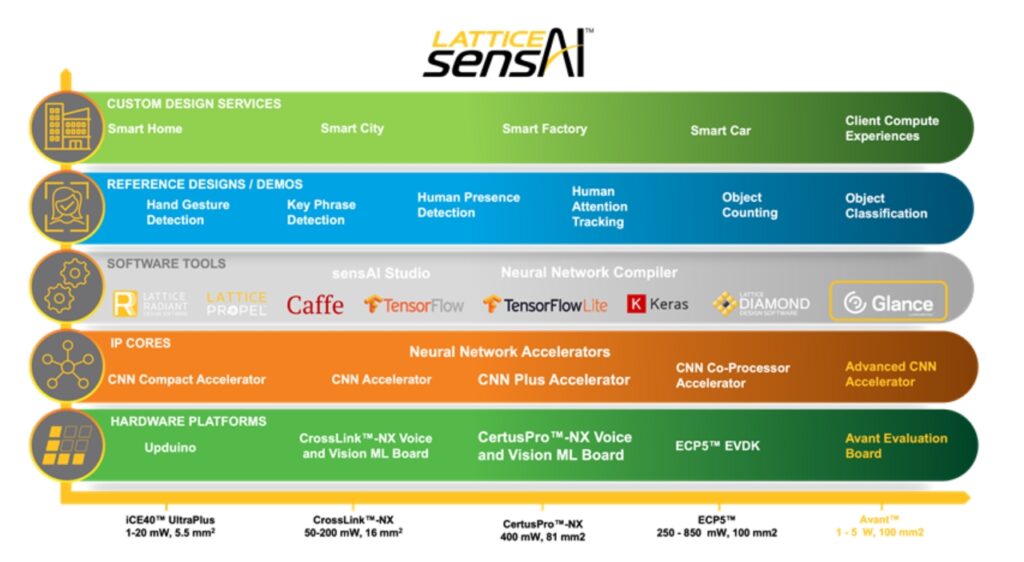

同樣以邊緣裝置所需的低功耗特性為主要訴求,專精FPGA技術的萊迪思半導體(Lattice Semiconductor)在2018年推出以sensAI為名,結合模組化硬體套件、神經網路IP、軟體工具、參考設計和客製化服務的「全套式」Edge AI解決方案,號稱可提供低至毫瓦(1mW)等級功耗、小尺寸(5.5~100 mm2)、低成本(量產價1~10美元)以及具備MIPI CSI-2、LVDS、GigE等豐富介面資源等優勢。

Lattice針對各種Edge AI應用提供結合軟硬體與設計服務的全套式sensAI解決方案。(圖片來源:Lattice Semiconductor)

在硬體部份的支援選項包括CrossLink-NX (採用FD-SOI製程)、ECP5/ECP5-5G與iCE40 UltraPlus系列不同運算/價格/功耗等級與功能選項的FPGA,可在邊緣裝置獨立運作,也可作為預處理器(preprocessor)搭配CPU/MPU/MCU扮演AI加速器角色。開發者可透過Lattice的sensAI Studio下載熱門應用案例的參考設計,並使用Radiant (支援iCE40 UltraPlus)或Diamond (支援CrossLink與ECP5)等軟體開發工具進行設計。

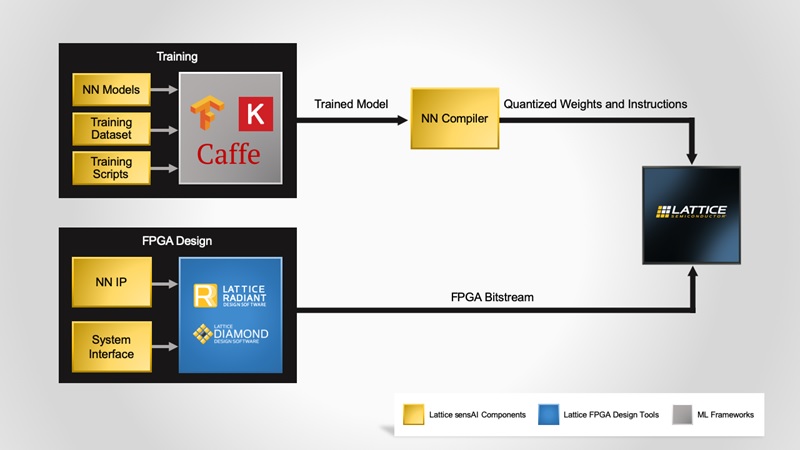

sensAI著重對現有IoT (即邊緣)裝置之感測器資料處理和分析的需求,涵蓋需要辨識使用者身份的智慧音箱、智慧門鈴,以及支援精準影像辨識的保全監控攝影機、工業用機器視覺、無人機視覺、ADAS等應用。將經過Tensorflow框架進行訓練的模型轉為TF Lite格式,可透過Lattice支援C++語言的Propel開發平台在FPGA構建SoC以部署終端應用。

Lattice針對Edge AI應用提供容易上手的開發流程。(圖片來源:Lattice Semiconductor)

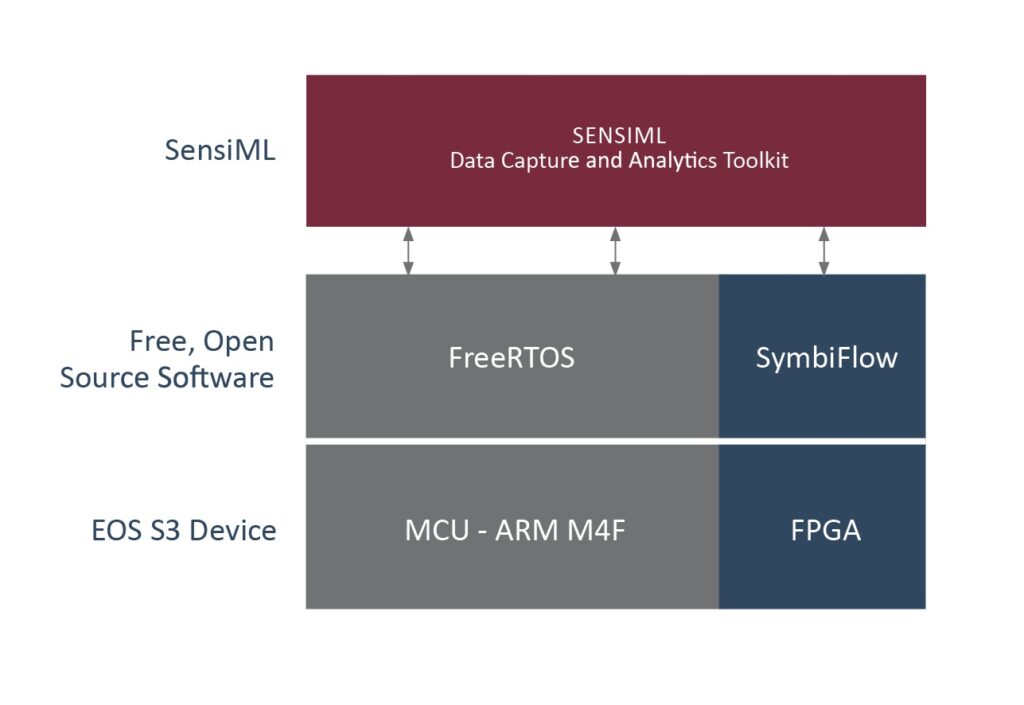

除了Lattice,另一家以低功耗FPGA為技術主力的供應商QuickLogic,除了在2015年就推出第一款結合嵌入式FPGA (eFPGA),可支援邊緣裝置語音辨識、AI推論應用的EOS S3系列低功耗MCU (採用Arm Cortex-4核心),該公司在2018年宣佈收購SensiML成為全資子公司,企圖透過結合開放性AutoML軟體工具平台與自家eFPGA IP,提供完整的端對端Edge AI解決方案,同時也攜手產業界其他廠商夥伴形成生態系,未來發展也相當值得注意。

QuickLogic結合SensiML打造完整端對端Edge AI部署解決方案。(圖片來源:QuickLogic)

無論是MCU/MPU或FPGA,市面上有越來越多各具特色的Edge AI解決方案與開發工具,接下來MakerPRO將會持續為社群讀者們報導最新相關訊息與技術發展,歡迎開發者們一起交流心得,或留言告訴我們你想知道的更多細節!

- 重磅宣告「邁入新階段」:Arm開賣AI資料中心CPU晶片 - 2026/03/25

- ADI:AI正加速邁向「實體智能」 - 2026/03/13

- 開拓GaN元件低電壓應用新戰場 EPC準備在AI時代大顯身手 - 2026/02/03

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!