半導體已成為讓這個世界正常運轉不可或缺的關鍵元素,從製造業自動化生產線、大型資料中心、支援5G高速行動通訊的基礎設施,擁有不同等級自動駕駛功能的大小車輛,以及各種內建人工智慧/機器學習(AI/ML)的裝置;這雖意味著一個持續蓬勃成長、商機無限的市場,卻也代表半導體晶片設計與驗證工程師正面臨越來越艱鉅的挑戰。

要克服眼前的挑戰,EDA供應商Cadence Design System資深副總裁暨系統與驗證事業部(SVG)總經理Paul Cunningham博士認為,除了利用最先進的EDA工具來協助工程師,對晶片設計業者來說,更重要的是思考工程團隊的任務重組以及心態上的調整。

Cadence Design System資深副總裁暨系統與驗證事業部(SVG)總經理Paul Cunningham博士。(圖片來源:Cadence)

「當前最先進的SoC內含電晶體數量達到上千億,該數字在這一個十年之內將輕易突破上兆;」在首度於台灣舉行的IC設計與驗證大會(DVCon Taiwan 2023)的專題演說中,Cunningham博士分享了他的觀察:「而且我們的半導體元件將變得更加異質結構,多顆裸晶以矽中介層堆疊在單一封裝中,這些3D IC帶來了100倍的元件複雜度。在此同時,每年的設計案數量可能是原來的4倍,這看起來像是工作量增加了400倍。」

但當然,一家公司不可能因此將工程團隊人力擴充400倍,更別說目前整體半導體領域正面臨人才短缺的窘境;為此,產業社群持續努力的一個目標是,如何讓一個工程師能做到原本可能需要100位工程師才做得了的事──這也是過去35年來Cadence的使命。

從電晶體、標準單元到RTL層級,透過一步步將積體電路個別功能區塊的設計抽象化,EDA工具帶來了革命性的方法,讓工程師能以Verilog硬體描述語言(HDL)創建電路,實現了晶片設計與驗證流程的自動化。

「如今撰寫RTL程式其實與軟體核心程式開發流程並沒有多大的差別,」Cunningham博士表示,HDL持續進化,現在工程師可以直接以C語言編譯RTL程式,而越來越豐富的SystemVerilog功能,加入了對更多更高階程式語言的支援,像是Perl Script,或是RISC-V處理器核心開發所使用的Chisel Script等,相較於以往純手動設計已經是上百倍、甚至上千倍的生產力提升。

現在,由AI技術所驅動的設計與驗證方法,勢必能再帶來一個10倍生產力的提升;不過他卻指出:「我不認為抽象化在提高設計生產力方面還能有多大的空間,當然,還是會有漸進式的改善,我們也會持續向前邁進,但在我看來,眼前一個更重要的思考方向是晶片設計工程師的任務重組(task restructuring)。」

提升生產力之外 使用AI工具更重要的是心態調整

「隨著AI出現,我們現在應該開始檢視設計與驗證工程師們是如何安排時間,了解他們的職務與日常工作時程,然後嘗試讓他們的工作升級;」Cunningham博士解釋,就像是電動工具的發明,AI將實現能承擔目前由人工進行之任務的強大工具,「但這並不是為了要取代人類。人類是具創造力、有深度的思想家,我們能把所經歷的不同事物連結在一起,我們可以專注於一件事情並且做得非常好。」

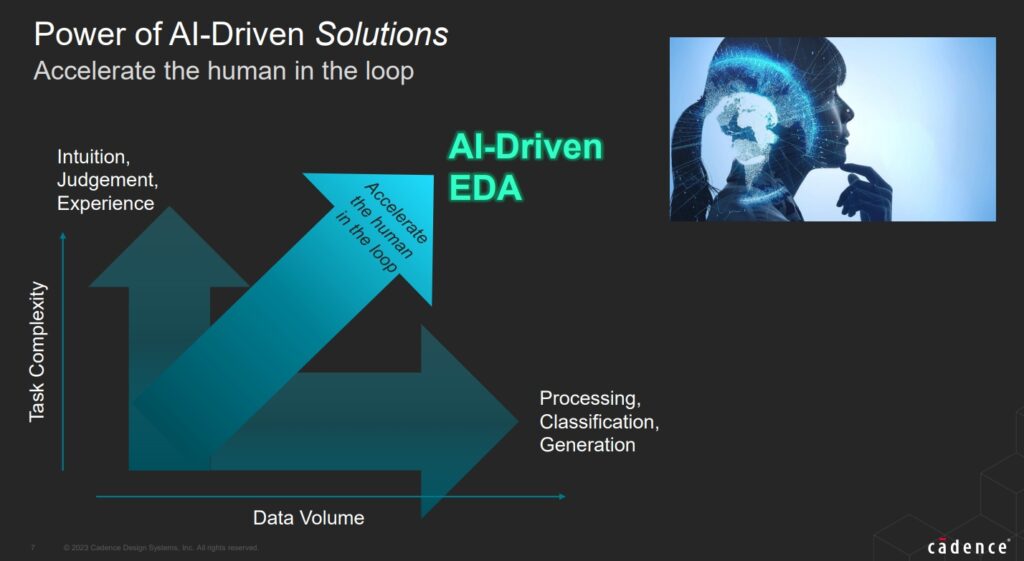

AI驅動解決方案並非要取代人類,而是為了加速人類的工作流程。(圖片來源:Cadence)

機器智慧的特性則是可以無限擴展,「就好像你可以盡可能給它很多眼睛跟耳朵;它們可以處理人類永遠無法處理的大量資料,能進行廣泛、水平化的連結並分類;也許有一天機器將擁有與人類相同水準的直覺與創造力,但在接下來的5到10年,AI能帶來的立即性好處,是為人類的創造力與日常生活帶來催化的效果。」

因此Cunningham博士表示,從EDA供應商的角度,利用AI來協助客戶解決最困難的設計挑戰當然是非常有趣的任務,不過他想傳達給客戶的概念是,AI工具更重要的功能是讓團隊人力有更好的配置:「想想你的大多數員工,可能是剛畢業的新鮮人,或是年資不到五年的新手,他們花最多時間在什麼工作上?要如何讓他們更有效率,擁有與資深工程師同樣的生產力?」

另一方面,在這個AI驅動EDA工具的新時代,工程師們還需要調整心態,大膽去嘗試創新的設計與驗證方法。「這些是非常不同的產品,並非開箱即用,但只要開始使用,就會看到實際上對生產力的提升是有效的;」對此Cunningham博士做了一個有趣的比喻:「如果你一輩子都在騎馬,某天第一次坐上汽車,也是哪裡都去不了。不過一旦你學會開車,你就會知道你一定會繼續這麼做,因為能跑得更遠、享受到比騎馬更多的樂趣。」

大數據平台結合多引擎、多次執行的新世代驗證流程

對目前大多數晶片設計驗證工程師來說,日復一日的工作通常是在不同的EDA工具引擎上,一次又一次執行專案以取得滿足客戶目標與最佳化PPA表現的結果。而AI技術能帶來的是多引擎、多次執行的設計與驗證流程,更重要的是能達到人力不能及的速度、覆蓋率以及跨時間的運作。而在這其中,大數據平台扮演了關鍵的角色。

「ChatGPT讓人覺得神奇,但如果沒有透過網際網路的開放存取,讓它能收集大量數據進行訓練,它可能就不會那麼神奇;」Cunningham博士表示,Cadence所創建的JedAI (Joint Enterprise Data AI)平台就是以這樣的概念為基礎,期望藉由一個具備開放性通用API的雲端資料庫,持續累積來自人類工程師的智慧結晶,透過大數據分析加速設計驗證流程,實現更高的生產力與設計品質。

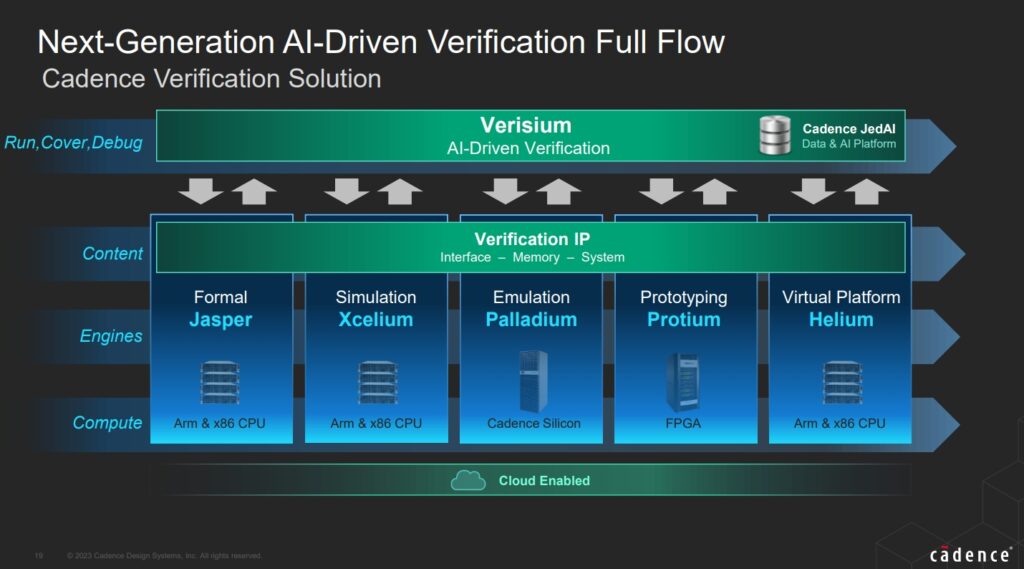

採用Spark框架的JedAI支援Python與C++語言,而Cadence在一年前發表的驗證平台Verisium奠基於其上,號稱完成了驗證工具從單引擎、單次執行晉級到多引擎、多次執行演算法的世代交替;透過採用該平台,各種驗證數據如波形、覆蓋範圍、驗證報告和文件皆能匯集到JedAI ,以利用機器學習模型從這些數據中挖掘出其他專有指標、啟用新工具,因此提高驗證效率。儘管這個新旅程才剛展開,根據Cunningham博士的分享,已有客戶透過採用Verisium平台,在不同的驗證步驟中取得3倍到高達60倍的不等的生產力提升。

Cadence結合AI與大數據平台的新一代驗證流程。(圖片來源:Cadence)

除了Verisium,Cadence的驗證流程工具還包括Xcelium邏輯模擬器(Logic Simulator)、Jasper形式驗證平台,還有硬體形式的Palladium Z2模擬平台、Protium X2原型驗證系統、Helium Studio系統虛擬/混合原型創建平台;這些解決方案將透過與AI引擎的結合,以及雲端運算環境帶來的彈性,將複雜系統的設計驗證推進下一個世代。

而就像是ChatGPT等大型語言模型,在IC設計領域是否能有真正「開放」的模型讓所有的設計工程師都能運用?這在特別注重矽智財(IP)保護的半導體產業確實會是個問題,對此Cunningham博士認為:「如果全世界的晶片與系統業者願意貢獻自家的資料成為集合智慧,那將會是非常非常強大的AI模型;而我確信無論是Cadence或其他業者都會非常樂意促成此事。」

然而目前的實際情況是,儘管有AI平台的輔助,Cadence也願意貢獻自家的IP,目前各家晶片業者仍是在封閉的環境中進行模型訓練,以確保設計機密不外流;而AI所創造的價值應該歸屬於運算系統擁有者還是資料的提供者,目前都還是一個爭論不休的社會議題。Cunningham博士坦言,「這真的不是我們自己可以決定,會非常非常困難。」

- 代理式AI與數位孿生正在重塑電子工程設計流程 - 2026/04/21

- 從大型GPU叢集到單機工作站:機器人強化學習的全新路徑 - 2026/04/20

- 高通與Snap宣佈擴大合作:2026可望成為消費性智慧AR眼鏡轉折點? - 2026/04/15

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!