作者:Bird

上篇文章【Maker電子學】SPI 界面解密—PART 2,我們聊了 SPI 的核心—移位暫存器的邏輯結構與它的工作原理,這次我們繼續來深入探討 SPI 運作時的訊號。

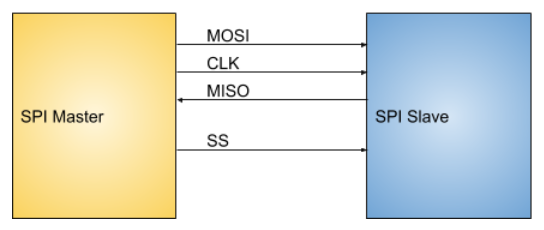

一對一

SPI 允許一對一、一對多的連接。這邊先來看一個最簡單的 case:一個 master 連接一個 slave(之前提過,這樣的 SPI 連接需要三到四個訊號):

- MOSI–master out slave in,從 master 送往 slave 的串列資料

- MISO–master in slave out,從 slave 送往 master 的串列資料

- CLK–用來驅動移位暫存器、取樣資料的 clock 訊號

- SS–slave select,用來選擇 slave 的訊號(在某些系統中可以省略)

(圖片來源:Bird 提供)

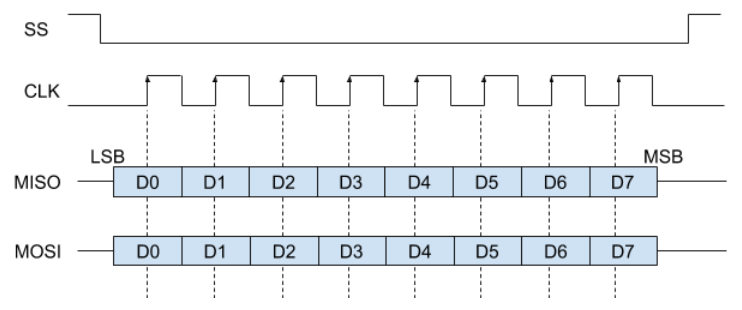

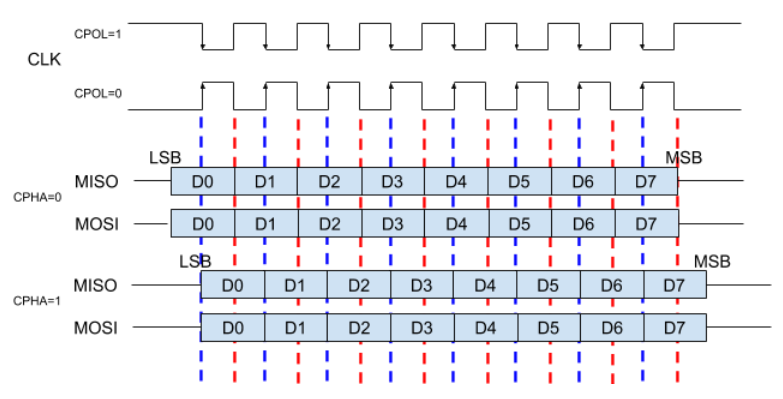

先來看一個典型的 SPI 時序圖:

(圖片來源:Bird 提供)

我們在上篇文章提過,移位暫存器裡面的 D 型正反器會在 clock 訊號的上升緣將資料鎖入正反器中,因此典型的 SPI 就是利用 8 個 clock 訊號的週期,傳輸一筆 8-bit 的資料。

SPI 有 MISO 和 MOSI 兩個訊號,分別負責 master 到 slave 與 slave 到 master 的傳輸,因此它是全雙工的介面(所謂全雙工就是能同時雙向傳輸)。

至於 SS 訊號則是 slave 用來通知 slave「嘿!我要開始一個傳輸週期了,請準備好」。 SPI 所有的傳輸都只能由 master 發起,不管是要寫入資料到 slave 還是從 slave 讀取資料,都只能由 master 控制,slave 是無法主動對 master 傳送資料的。

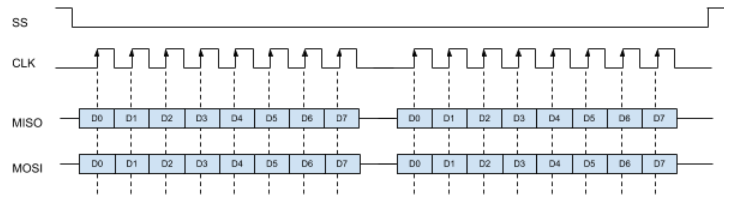

SPI 所有的資料傳輸都以 8-bit(1 個 byte)為基本單位(可能是因為它是在 8-bit 微處理器那個年代發明的),但是一個傳輸週期中可以包含不止一個 byte,它可以是兩個 bytes(16-bit)、三個 bytes(24-bit),甚至更多。在這種多個 byte 的傳輸週期中,SS 腳會一直維持在 low,直到所有的資料都傳輸完,才會恢復到 idle 的狀態。

典型的 2-byte SPI 傳輸時序圖(圖片來源:Bird 提供)

SPI 的協定說明到這裡就差不多啦!事實上 Motorola 當年制定 SPI 的協定時,真的就只說這麼多。它簡單來說就是個用來節省接腳、取代並列介面的同步式串列介面,至於介面上要用來傳輸什麼、一個傳輸週期要傳幾個 byte、每個 byte 有沒有各自的意義( address、暫存器、 memory 編號等),其實都不在 SPI 的協定中,這些更高階、更細節的協定,其實取決於你連接在 SPI 上的週邊裝置而定。

如果你連接了一個 SPI 介面的 flash memory,你就得參考 SPI flash memory 的規格書,使用它的 SPI 協定與它溝通,比方說寫一個內容是 0x06 的 byte 到 SPI flash memory,就代表打開它的 write enable,使它可以寫入,這就是一個 1-byte 的傳輸週期;如果寫一個內容是 0x05 的 byte 到 SPI flash,然後接著讀一個 byte 回來,就代表讀回它的狀態暫存器,這也就是一個 2-byte 的傳輸週期。

極性與相位

經過了幾十年的演進,SPI 其實也慢慢發展出一些與當初制定的標準略有不同的協定。

雖然這個世界上絕大多數的移位暫存器或 D 型正反器都是在 clock 訊號的上升緣鎖定資料,但就是有一些比較搞怪的周邊元件會在 clock 訊號的下降緣鎖定資料;遇到這種非典型的 SPI 裝置,除了在 CLK 訊號上加個 inverter 外,還有別的方法可以解決嗎?

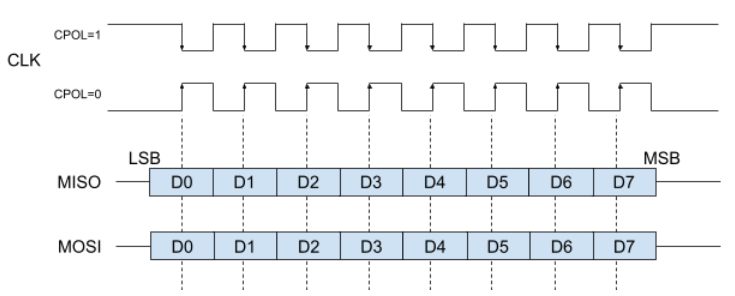

為了因應各種 SPI 周邊裝置,事實上現在的微處理器都提供很多 SPI 相關的設定,讓你可以微調 SPI 的訊號格式,以適應各種周邊。以這個 clock 訊號的上升緣取樣或下降緣取樣的問題而言,大部分的微處理器都提供了一個稱為「CPOL」(clock polarity,意即 clock 訊號的極性)的設定,可以用來決定在 clock 訊號的上升緣或下降緣取樣資料。

(圖片來源:Bird 提供)

- 當 CPOL = 0 時,就如同我們之前說明過的典型 SPI 訊號,CLK 在不動作時維持在 low,資料取樣在 CLK 的上升緣發生

- 當 CPOL = 1 時,CLK 不動作時維持在 high,資料取樣在 CLK 的下降緣發生

除了 CPOL 外,還有另一個在微處理器上常見的 SPI 設定—CPHA(clock phase),它主要用來控制 clock 與資料取樣點之間的相位關係。

- 當 CPHA = 0 時,SPI 的第一個 bit 傳輸會發生在 clock 訊號開始變化的第一個邊緣,至於這第一個邊緣是上升緣還是下降緣,取決於 CPOL 的設定。當 CPOL = 0 是,由於 clock 不動作時是維持在 low,一旦它開始變化,一定是要變成 high,因此它的第一個變化一定是上升緣;CPOL = 1 時亦同

- 當 CPHA = 1 時,SPI 的第一個 bit 傳輸會發生在 clock 訊號開始變化的第二個邊緣。由於 clock 訊號是交替在 high 和 low 之間變動的,如果第一個邊緣是上升緣,第二個邊緣就會是下降緣;如果第一個邊緣是下降緣,第二個邊緣就是上升緣,因此在上升緣或下降緣取樣資料,除了要看 CPOL,也要看 CPHA 的設定

我們把 CPOL 和 CPHA 的四種組合畫在同一張圖:

(圖片來源:Bird 提供)

你也可以把 CPHA 的功能想像成:當 CPHA = 1 時,資料取樣點會延後半個 clock cycle。CPHA = 1 的這種邏輯常常用於一對一的 SPI,來傳輸不使用 SS 訊號的周邊裝置,它用 SPI clock 的第一個變化緣來「喚醒」周邊裝置,告訴它要準備好接受接下來的傳輸,然後才在 clock 的第二個變化緣開始傳輸資料。

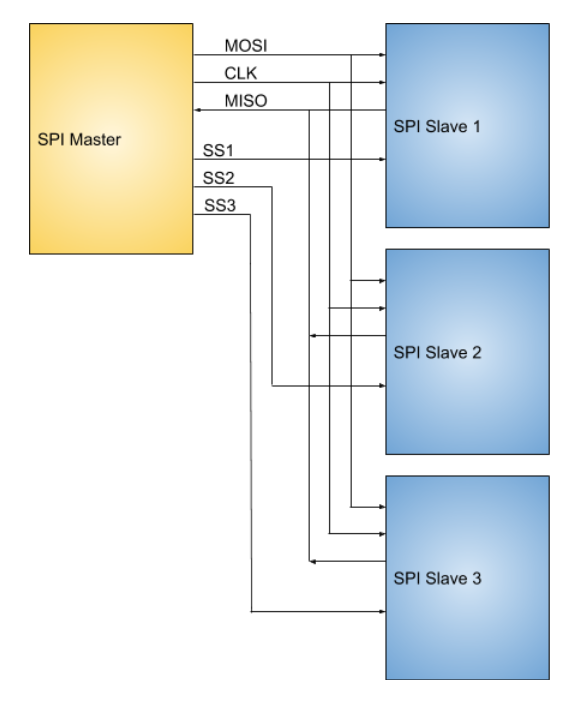

一對多

接下來我們看看 SPI 一對多的傳輸要怎麼進行。

在一對多的模式下,所有 SPI slave 的 MOSI、MISO、CLK 訊號通通都並聯在一起,才與 master 相接,但最重要的是,master 必須為每一個 slave 準備一個 SS 訊號,用這個 SS 訊號來選擇現在是要和哪一個 slave 溝通。

這裡要特別強調的是,SPI 並沒有「裝置地址」或「裝置編號」的觀念,它不像 I2C 或 Modbus/RS-485 那樣在同一個 bus 上可以透過協定中的裝置地址來點名哪個 slave 要接受指令。沒有!SPI 沒有裝置地址,master 用來在眾多 slave 裝置中選妃的方法,就是每個裝置上專屬的 SS 訊號。

對 master 而言,MOSI、CLK 是輸出腳,因此 slave 端的 MOSI、CLK 對 master 來說是高阻抗輸入,一對多的接法沒有問題,但 MISO 是 slave 的輸出腳,如果同時有一個以上的 slave 打開 MISO 的輸出,就好像把兩隻輸出腳接在一起,一定會發生邏輯衝突,因此大部分可以運作在一對多模式下的 SPI 周邊,都會用 SS 腳來控制 MISO 的輸出狀況(當 SS 為 high,也就是裝置沒有被選到時,MISO 腳會維持高阻抗;當 SS 變成 low,表示這個 slave 被點檯了,它就會打開 MISO 的輸出驅動電路)。

(圖片來源:Bird 提供)

如果 SPI master 沒有拉低任何一支 SS 接腳選擇任何一個 slave,就代表 MISO 這條線上沒有任何驅動源(此時所有 slave 的 MISO 都在高阻抗狀態;master 的 MISO 因為是輸入腳所以本來就是個高阻抗輸入),整條線就會處在一個隨風飄蕩、隨波逐流的完全高阻抗狀態。

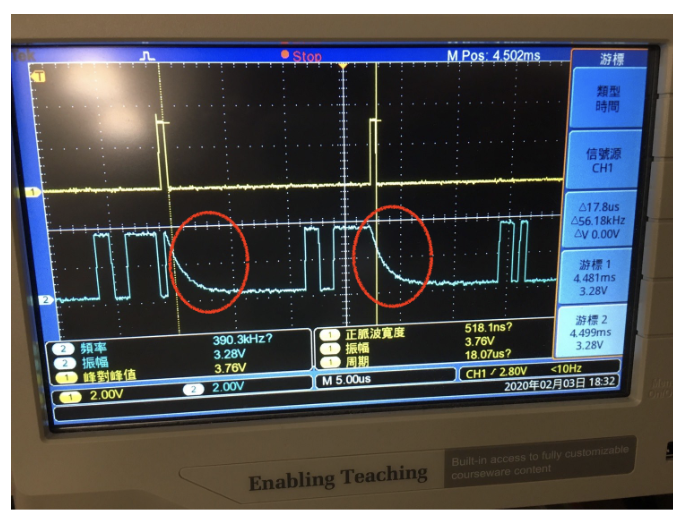

有時候我們會在示波器上看到 MISO 出現這樣的波形:

(圖片來源:Bird 提供)

紅色圈圈的地方會看到 MISO 呈現一個不像邏輯訊號的狀態,以一個很醜的樣子緩慢下降。事實上這是因為 master 結束一個傳輸週期,放掉 SS 訊號後,slave 乖乖聽話把 MISO 放手變成高阻抗,而 MISO 上又沒有其它的驅動源來決定它的狀況,因此就靠著各裝置之間高阻抗的平衡決定它最後的歸屬。

在這個例子中,平衡後的結果大概是個 weak pull down,所以 MISO 在被 slave 放開之後它就用一個緩慢的速度被拉到 low,而形成這樣一個醜醜的波形。

那這樣會有問題嗎?多半不會,因為當 master 放開 SS 時,就代表它已經不再對 slave 感興趣,因此當然不會再去在意 MISO 上的邏輯狀態。如果你不希望 MISO 上出現這樣的波形,可以在 MISO 上加一個 4.7 KΩ 到 10 KΩ 左右的 weak pull-up 或 pull-down 電阻,用來決定當 MISO 被眾人放棄時它該是 high 還是 low。

小結

這次我們詳細解說了 SPI 的實體通訊協定訊號與它們的運作方式,下一回我們將進入 SPI 的實際應用,來看看要如何利用 SPI 和其他週邊裝置溝通。

(責任編輯:賴佩萱)

- 【Maker電子學】Flash 記憶體的原理與應用—PART22 - 2025/02/27

- 【Maker電子學】Flash 記憶體的原理與應用—PART21 - 2025/02/21

- 【Maker電子學】Flash 記憶體的原理與應用—PART20 - 2025/01/24

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!