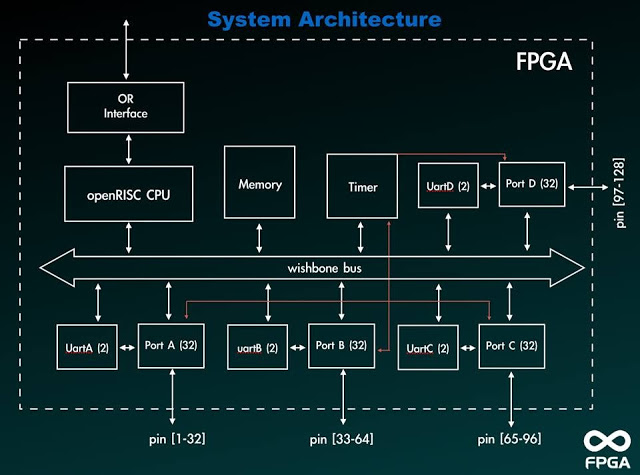

底下的圖片是一個再基礎不過的系統。一顆CPU配上該有的輸出入介面與記憶體架構。這是我未來的Open Source Hardware的基底,同時會把基本的系統軟體與工具鍊也“順便”完成了。

為什麼要做這種這麼“基礎”的東西?不是應該要用ARM based的嗎?要不然簡單的用現成的Arduino也行?

我想這個時候做這個一定會被酸的。可是各位有沒有想過,十多年前的許多人都用WinCE,而笑用Linux做產品不穩定,沒保障? 二十多年前若是說有一家做32-bit小CPU的公司會在今天讓Intel不知道怎麼辦,你一定不相信?當初笑的後來笑不出來,不相信的都乖乖每年繳錢。

問題是,我們在教學的過程裡,發現這些很“基礎”的東西學生能學會的不多,大家都被ARM給”豢養”著了,沒有了成套的“開源”工具鍊,很多學生,甚至老師,應該就被斷手斷腳,動彈不得了。很多事都無法從底層來解決問題,問題是很多問題都發生在系統底層。事實上,我自己也不會一大堆ARM的工具鍊,但是我已經是舊時代的產物,不會不奇怪,因為我做的都是很“基礎”的東西,之所以會跳出來做一個這樣子的系統,是我的心中深層的恐懼。

想像一下過去幾十年,台灣很大層面都是被Intel與ARM所宰制,過去是乖乖買Intel的x86CPU,現在是乖乖交錢給ARM。不管哪一種,錢都繳得還蠻甘願的。

我也知道在當今不管是業界還是學術界的氛圍,這麼做其實也改變不了什麼,那麼為什麼還要做呢?

其一是希望學校的計算機組織、微算機、作業系統等課程可以上得扎實一點。這個開源工具可以讓大家做到這點。若有老師願意拿去用在教學上,我們將會有整套的教材。

其二是我自己的研究需要。前面說過,我是做晶片內記憶體(on-chip memory)架構管理的。過去,在效能評估上,多數論文是用一個cost function來估測EDP(energy delay product)的,但是當面對外部是DDR時,資料存取的timing是難以估到100%的。所以為了我的研究數據具備100%公信力,我們乾脆自己刻一個完整系統。從硬體與OS(RTOS),且更進一步連TLB、MMU等等都照個我們論文的要求把OpenRISC都改了。而且做到可以紀錄並視覺化每一個指令在計算與資料存取的過程,可以重播、倒帶、精確統計等等。不管做研究的、教學的,或是愛玩的駭客,我希望提供給大家的是一套完整的工具,讓你愛幹嘛就幹嘛!完全Open and free 。

在這個基礎上,我們也做OpenCL的工具,所以CL的Kernel functions可以跑在OpenRISC上。因此,從OpenCL上可以連想到的是,我們在Xilinx的V7 FPGA上,可以放入遠超過500顆OpenRISC,透過DDR3當作共享記憶體來彼此溝通,即使是一千元一顆的Xilinx低階的FPGA也可以放1~4顆OpenRISC。而且從撰寫多核心程式、compile、booting一直到執行,這一連串所需的工具(含QT Based的GUI工具)都幫大家準備好了。

而且不僅有提供使用手冊,還有技術手冊與教學投影片,讓你可以進來一起改、一起玩。因為,我們知道我們不可能把每一件事都做到好,我們需要夥伴,而夥伴就是願意一起來玩的各位了。我們需要社群的力量,在外面一定有比我們更厲害的高手可以來幫我們。

我相信,我們這麼誠心誠意想要完成這麼一件事,全宇宙都會來幫我們才對。

每一個時代都有每一個時代看起來愚笨的人們,而往往只有被當時說是愚笨的人有更大的機會做一些不一樣的事來改變這個世界。

賈伯斯不是說過要,Think Different嗎?

假如我說,我要讓不會電路設計的人也可以自己設計自己要用的處理器,然後在上面開發自己想要的應用,請不要笑我,因為這件事實現的日子不是今年,就是明年。

來吧!

延伸閱讀

訂閱MakerPRO知識充電報

與40000位開發者一同掌握科技創新的技術資訊!